GLEN MÉVEL, Inria, Université Paris-Saclay, CNRS, Laboratoire de recherche en informatique, France JACQUES-HENRI JOURDAN, Université Paris-Saclay, CNRS, Laboratoire de recherche en informatique FRANÇOIS POTTIER, Inria, France

Multicore OCaml extends OCaml with support for shared-memory concurrency. It is equipped with a weak memory model, for which an operational semantics has been published. This begs the question: what reasoning rules can one rely upon while writing or verifying Multicore OCaml code? To answer it, we instantiate Iris, a modern descendant of Concurrent Separation Logic, for Multicore OCaml. This yields a low-level program logic whose reasoning rules expose the details of the memory model. On top of it, we build a higher-level logic, Cosmo, which trades off some expressive power in return for a simple set of reasoning rules that allow accessing nonatomic locations in a data-race-free manner, exploiting the sequentially-consistent behavior of atomic locations, and exploiting the release/acquire behavior of atomic locations. Cosmo allows both low-level reasoning, where the details of the Multicore OCaml memory model are apparent, and high-level reasoning, which is independent of this memory model. We illustrate this claim via a number of case studies: we verify several implementations of locks with respect to a classic, memory-model-independent specification. Thus, a coarse-grained application that uses locks as the sole means of synchronization can be verified in the Concurrent-Separation-Logic fragment of Cosmo, without any knowledge of the weak memory model.

CCS Concepts: • Theory of computation → Separation logic; Program verification.

Additional Key Words and Phrases: separation logic, program verification, concurrency, weak memory

#### **ACM Reference Format:**

Glen Mével, Jacques-Henri Jourdan, and François Pottier. 2020. Cosmo: A Concurrent Separation Logic for Multicore OCaml. *Proc. ACM Program. Lang.* 4, ICFP, Article 96 (August 2020), 29 pages. https://doi.org/10. 1145/3408978

We are all in the gutter, but some of us are looking at the stars. - Oscar Wilde

# **1 INTRODUCTION**

Multicore OCaml [Dolan et al. 2018a] extends the OCaml programming language [Leroy et al. 2019] with support for shared-memory concurrency. It is an ongoing experimental project: at the time of writing, although preparations are being made for its integration into mainstream OCaml, this has not yet been done. Nevertheless, Multicore OCaml has a well-defined semantics: in particular, its *memory model*, which specifies how threads interact through shared memory locations, has been published by Dolan et al. [2018b]. Therefore, one may already ask: what reasoning rules can or should a Multicore OCaml programmer rely upon in order to verify their code?

Multicore OCaml's memory model is *weak*: it does not enforce sequential consistency [Lamport 1979]. That is, the execution of a program is not necessarily an interleaving of the actions performed by its threads while interacting with a central shared memory. Many mainstream programming

Authors' addresses: Glen Mével, Inria, Université Paris-Saclay, CNRS, Laboratoire de recherche en informatique, 91405, Orsay, France, glen.mevel@inria.fr; Jacques-Henri Jourdan, Université Paris-Saclay, CNRS, Laboratoire de recherche en informatique, 91405, Orsay, jacques-henri.jourdan@lri.fr; François Pottier, Inria, France, françois.pottier@inria.fr.

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for third-party components of this work must be honored. For all other uses, contact the owner/author(s).

© 2020 Copyright held by the owner/author(s). 2475-1421/2020/8-ART96 https://doi.org/10.1145/3408978 languages, including lower-level languages such as C11 [Batty et al. 2011; Lahav et al. 2017] and higher-level languages such as Java [Manson et al. 2005; Lochbihler 2012; Bender and Palsberg 2019], adopt weak memory models, because this allows compilers to perform more aggressive software optimizations and to better exploit hardware optimizations. Multicore OCaml follows this trend. Although it is expected that most application programmers will not need to worry about weak memory, because they will rely on a library of concurrent data structures written by domain experts, adopting a weak memory model allows said experts to write more efficient code—if they know what they are doing, that is!

We believe that there is a need for a set of reasoning rules—in other words, a program logic—that both populations of programmers can rely upon. Concurrency experts, who wish to implement efficient concurrent data structures, must be able to verify that their code is correct, even though they have removed as many synchronization operations as they thought possible. Furthermore, they must be able to verify that their code implements a simple, high-level abstraction, thereby allowing application programmers, in turn, to use it as a black box and reason about application code in a simple manner. In short, the system must allow compositional reasoning, and must allow both low-level reasoning, where the details of the Multicore OCaml memory model are apparent, and high-level reasoning, which is independent of this memory model.

Others before us have made a similar argument. For instance, Sieczkowski et al. [2015] propose iCAP-TSO, a variant of Concurrent Separation Logic that is sound with respect to the TSO memory model. While iCAP-TSO allows explicit low-level reasoning about weak memory, it also includes a high-level fragment, the "SC logic", whose reasoning rules are the traditional rules of Concurrent Separation Logic. These rules, which are independent of the memory model, require all direct accesses to memory to be data-race-free. Therefore, they require synchronization to be performed by other means. A typical means of achieving synchronization is to implement a lock, a concurrent data structure whose specification can be expressed in the SC logic, but whose proof of correctness must be carried out at the lower level of iCAP-TSO. As another influential example, Kaiser et al. [2017] follow a similar approach: they instantiate Iris [Jung et al. 2018b], a modern descendant of Concurrent Separation Logic, for a fragment of the C11 memory model. This yields a low-level "base logic", on top of which Kaiser et al. proceed to define several higher-level logics, whose reasoning rules are easier to use. Our aim, in this paper, is analogous. We wish to allow the verification of a low-level concurrent data structure implementation, such as the implementation of a lock. Such a verification effort must take place in a program logic that exposes the details of the Multicore OCaml memory model. At the same time, we would like the program logic to offer a high-level fragment that is independent of the memory model and in which data-race-free accesses to memory, mediated by locks or other concurrent data structures, are permitted.

Compared with other memory models in existence today, the Multicore OCaml memory model is relatively simple. Only two kinds of memory locations, known as "nonatomic" and "atomic" memory locations, are distinguished. Every program has a well-defined set of permitted behaviors. In particular, data races on nonatomic memory locations are permitted, and have "limited effect in space and in time" [Dolan et al. 2018b]. This is in contrast with the C11 memory model, where racy programs are deemed to have "undefined behavior", therefore must be ruled out by a sound program logic. Dolan et al. [2018b] propose two definitions of the Multicore OCaml memory model, and provide an informal proof that these definitions are equivalent. One definition takes the form of an operational semantics, where the execution of the program is in fact an interleaving of the executions of its threads. These threads interact with a memory whose behavior is more complex than usual, and whose description involves concepts such as *time stamps*, *histories*, *views*, and so on (§2). The other definition is an axiomatic semantics, where a "candidate execution" takes the form of a set of memory events and relations between them, and an actual execution is a candidate

execution that respects certain conditions, such as the acyclicity of certain relations. In this paper, we take Dolan *et al.*'s operational semantics, which we recall in Section 2, as a foundation. We instantiate Iris for this operational semantics. This yields a low-level logic, BaseCosmo (§3), whose reasoning rules expose the details of the Multicore OCaml memory model. Because of this, these rules are not very pleasant to use. In particular, the rules that govern access to nonatomic memory locations are rather unwieldy, as they expose the fact that the store maps each nonatomic location to a history, a set of write events. In order to facilitate reasoning, on top of BaseCosmo, we build a higher-level logic, Cosmo (§4), whose main features are as follows:

- Cosmo forbids data races on nonatomic locations. Data races on atomic locations remain permitted: atomic locations are in fact the sole primitive means of synchronization. This design decision allows Cosmo to offer a simplified set of reasoning rules, including:

- standard, straightforward rules for data-race-free access to nonatomic locations;

- standard, straightforward rules for possibly racy access to atomic locations, with the ability

of exploiting the sequentially-consistent behavior of these locations; and

- nonstandard yet arguably simple rules for reasoning about the release/acquire behavior of atomic locations.

The last group of rules allow transferring a "view" of the nonatomic memory from one thread to another. By exploiting this mechanism, one can arrange to transfer an arbitrary assertion P from one thread to another, even when the footprint of P involves nonatomic memory locations. This feature is used in all of our case studies (§5).

Although views have appeared in several papers [Kaiser et al. 2017; Dang et al. 2020], letting the user reason about release/acquire behavior in terms of abstract views seems novel and simpler than previous approaches. In particular, we claim that combining objective invariants and the axiom SPLIT-SUBJECTIVE-OBJECTIVE yields a simple reasoning scheme, which could be exploited in logics for other weak memory models.

• Cosmo offers a high-level fragment where reasoning is independent of the memory model, that is, a fragment whose reasoning rules are those of traditional Concurrent Separation Logic. In this fragment, there is no notion of view. This fragment consists at least of the rules that govern access to nonatomic locations and can be extended by allowing the use of concurrent data structures whose specification is independent of the memory model and whose correctness has been verified using full Cosmo. The spin lock and ticket lock (§5) are examples of such data structures: their specification in Cosmo is the traditional specification of a lock in Concurrent Separation Logic [Gotsman et al. 2007; Hobor et al. 2008]. Thus, Cosmo contains traditional Concurrent Separation Logic, and allows reasoning about coarse-grained concurrent programs where all accesses to memory locations are mediated via locks.

We illustrate the use of Cosmo via several case studies (§5), including a spin lock, a ticket lock, and a lock based on Peterson's algorithm. All of our results, including the soundness of Cosmo and the verification of our case studies, are machine-checked in Coq. Our proofs can be browsed in the accompanying artifact and are also available from our repository [Mével et al. 2020].

### 2 MULTICORE OCAML

In this section, we recall the Multicore OCaml memory model and present the syntax and operational semantics of a core calculus that is representative of the Multicore OCaml programming language. We start by describing interactions with the memory by the memory subsystem (§2.1), and then we present the reduction rules of the programming language itself (§2.2).

$a \in \operatorname{Loc}_{\operatorname{NA}}$   $A \in \operatorname{Loc}_{\operatorname{AT}}$   $t \in \operatorname{Time} \triangleq \mathbb{Q} \cap [0, \infty)$   $h \in \operatorname{Hist} \triangleq \operatorname{Time} \xrightarrow{\operatorname{fin}} \operatorname{Val}$   $\mathcal{V}, \mathcal{W}, \mathcal{G} \in \operatorname{View} \triangleq \operatorname{Loc}_{\operatorname{NA}} \xrightarrow{\operatorname{aez}} \operatorname{Time}$   $\sigma \in \operatorname{Store} \triangleq (\operatorname{Loc}_{\operatorname{NA}} \xrightarrow{\operatorname{fin}} \operatorname{Hist}) \times (\operatorname{Loc}_{\operatorname{AT}} \xrightarrow{\operatorname{fin}} \operatorname{Val} \times \operatorname{View})$

Fig. 1. Semantic objects: locations, time stamps, histories, views, stores.

# 2.1 Memory Model

In this section, we recall Dolan et al.'s definition of the Multicore OCaml memory model (2018b) and extend it with memory allocation and CAS, which do not appear in Dolan et al.'s paper. We first define a number of semantic objects (Figure 1), then describe the behavior of the memory subsystem (Figure 2). At this point, we assume a set VAL of values, which is defined later on (§2.2).

2.1.1 Locations. A memory location has one of two possible kinds, fixed throughout its lifetime: it is either *nonatomic* or *atomic*. We write *a* for a nonatomic location and *A* for an atomic one.

2.1.2 Time Stamps. We use time stamps t to describe the behavior of reads and writes at nonatomic memory locations. They belong to  $\mathbb{Q} \cap [0, \infty)$ , the set of the nonnegative rational numbers. This set is infinite, totally ordered, and admits a minimum element 0, which is used for initial writes, and only for initial writes. It is worth noting that the meaning of time stamps is purely "per location": that is, the time stamps associated with two write events at two distinct locations are never compared.

2.1.3 *Histories.* A *history h* is a finite map of time stamps to values. It represents the history of the write events at a single nonatomic memory location. If desired, a history can be also be viewed as a set of pairs of a time stamp and a value, that is, a set of write events, under the constraint that no two events have the same time stamp. Naturally, a read instruction at a nonatomic memory location must read from one of the write events in the history of this location, and a write instruction must extend the history of this location with a write event at a previously-unused time stamp. In either case, which time stamp may be chosen depends on the "view" of the active thread, described next.

2.1.4 Views. A view  $\mathcal{V}$ , referred to as a "frontier" by Dolan et al. [2018b], is a total mapping of nonatomic memory locations to time stamps that is *almost everywhere zero* ("aez" for short), that is, whose value is zero everywhere except a finite set of locations. Each thread has a view, which evolves over time. The view of a thread maps each nonatomic memory location to (the time stamp of) the most recent write event at this location this thread is aware of. The view of the active thread imposes a constraint on the behavior of reads and writes at nonatomic memory locations (§2.2.2).

The order on time stamps gives rise to a partial order on views: by definition, the view inequality  $\mathcal{V}_1 \sqsubseteq \mathcal{V}_2$  holds if and only if, for every nonatomic memory location *a*, the time stamp inequality  $\mathcal{V}_1(a) \leq \mathcal{V}_2(a)$  holds. This order can be thought of as an *information* order: if  $\mathcal{V}_1 \sqsubseteq \mathcal{V}_2$  holds, then a thread with view  $\mathcal{V}_2$  has more information (is aware of more write events) than a thread with view  $\mathcal{V}_1$ . Equipped with this order, views form a bounded semilattice. Its minimum element is the *empty view*  $\perp$ , which maps every nonatomic memory location to the time stamp 0. Its join operation is pointwise maximum: that is,  $\mathcal{V}_1 \sqcup \mathcal{V}_2$  is  $\lambda a$ . max ( $\mathcal{V}_1(a), \mathcal{V}_2(a)$ ).

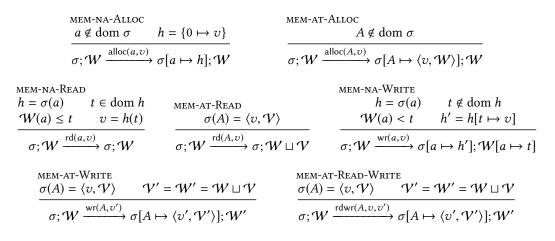

Fig. 2. Operational behavior of the memory subsystem:  $\sigma; \mathcal{W} \xrightarrow{m} \sigma'; \mathcal{W}'$

2.1.5 Stores. A store  $\sigma$  is a pair of a nonatomic store and an atomic store. A nonatomic store  $\sigma_{na}$  is a finite map of nonatomic memory locations to histories: as suggested earlier, each nonatomic memory location is mapped to a history of all write events at this location. An *atomic store*  $\sigma_{at}$  is a finite map of atomic memory locations to pairs of a value and a view. Indeed, atomic memory locations in Multicore OCaml serve two purposes, which are conceptually independent of one another. On the one hand, each atomic memory locations have sequentially consistent semantics. On the other hand, each atomic memory location stores a view, that is, a certain amount of information about the nonatomic store. This view is read and updated by atomic read and write instructions, thereby giving atomic memory locations a "release/acquire" semantics.

2.1.6 The Memory Subsystem. To complete the definition of the Multicore OCaml memory model, there remains to give an operational description of the behavior of the memory subsystem. This is done via a labelled transition system, that is, a relation  $\sigma; \mathcal{W} \xrightarrow{m} \sigma'; \mathcal{W}'$ , which describes how the shared global store  $\sigma$  and the view  $\mathcal{W}$  of the active thread evolve through a memory event m, yielding an updated store  $\sigma'$  and an updated view  $\mathcal{W}'$ . The syntax of memory events is as follows:

$m ::= \varepsilon \mid \operatorname{alloc}(a, v) \mid \operatorname{rd}(a, v) \mid \operatorname{wr}(a, v) \mid \operatorname{alloc}(A, v) \mid \operatorname{rd}(A, v) \mid \operatorname{wr}(A, v) \mid \operatorname{rdwr}(A, v, v')$

These memory events also appear in the definition of the semantics of Multicore OCaml expressions (§2.2.2). Thus, they form a language by which the expression and memory subsystems communicate.

The rules that define the relation  $\sigma$ ;  $\mathcal{W} \xrightarrow{m} \sigma'$ ;  $\mathcal{W}'$  (Figure 2) can be briefly described as follows. When a fresh nonatomic memory location is allocated (MEM-NA-ALLOC), its history consists of a single write event at time stamp 0. This guarantees that a read of this location will succeed, even if the reading thread has not synchronized with the thread where allocation was performed.

As suggested earlier (§2.1.4), the view of the active thread imposes a constraint on the behavior of read and write instructions at nonatomic memory locations. A read instruction at location a(MEM-NA-READ) cannot read from an outdated write event, therefore must read from an event whose time stamp t is no less than  $\mathcal{W}(a)$ . Both  $\mathcal{W}(a) = t$  and  $\mathcal{W}(a) < t$  are permitted: the latter case allows a thread to read from a write event of which it is not yet aware. A nonatomic read instruction does *not* update the view of the active thread. A write instruction at location a (MEM-NA-WRITE) cannot produce an outdated write event, therefore must use a time stamp t greater than  $\mathcal{W}(a)$ . The

Glen Mével, Jacques-Henri Jourdan, and François Pottier

| $b \in \{ false, true \}$                                                                                                               | — Boolean values                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| $n \in \mathbb{Z}$                                                                                                                      | <ul> <li>integer values</li> </ul>                           |

| $v ::= \mu f . \lambda x. e \mid () \mid b \mid n \mid a \mid A \mid (v,, v)$                                                           | — values                                                     |

| $⊙$ ∈ { && ,    , +, -, }                                                                                                               | <ul> <li>primitive operations (of arity 2)</li> </ul>        |

| <i>e</i> ::=                                                                                                                            | – expressions:                                               |

| $x \mid \mu f. \lambda x. e \mid e e$                                                                                                   | $-\lambda$ -calculus with recursive functions                |

| $  ()   b   n   e \odot e$                                                                                                              | <ul> <li>primitive values and operations</li> </ul>          |

| if e then e else e                                                                                                                      | <ul> <li>– conditional</li> </ul>                            |

| let x = e in e                                                                                                                          | — sequencing                                                 |

| (e,,e)  let $(x,,x) = e$ in $e$                                                                                                         | — tuples                                                     |

| fork e                                                                                                                                  | <ul> <li>spawning a new thread</li> </ul>                    |

| $ a $ new <sub>na</sub> $e  !_{na} e   e :=_{na} e$                                                                                     | <ul> <li>operations on nonatomic memory locations</li> </ul> |

| $ A  \operatorname{new}_{\operatorname{at}} e   !_{\operatorname{at}} e   e \coloneqq_{\operatorname{at}} e   \operatorname{CAS} e e e$ | <ul> <li>operations on atomic memory locations</li> </ul>    |

Fig. 3. Multicore OCaml: Syntax

new time stamp must be fresh (that is, not in the domain of h), but there is no requirement for t to be greater than every time stamp in the domain of h. The history of location a and the view of the active thread are updated so as to include the new write event.

Allocating a fresh atomic memory location (MEM-AT-ALLOC) causes it to be initialized with the value v provided by the allocation instruction and with the view W of the active thread. When reading an atomic memory location (MEM-AT-READ) the view V stored in this location is merged into the view of the active thread, reflecting the idea that the active thread acquires information via this read operation. Writing an atomic memory location (MEM-AT-WRITE) overwrites the value v stored at this location with the new value v' and updates the view V stored at this location by merging the view W of the active thread into it, reflecting the idea that the active thread releases information via this write operation. At the same time, the view of the active thread is updated; indeed, an atomic write has both a "release" and an "acquire" effect. The rule MEM-AT-READ-WRITE models a successful CAS instruction. It which combines the effects of a read and a write in a single atomic step. An unsuccessful CAS instruction behaves like an atomic read.

As Multicore OCaml is equipped with a garbage collector, there is no explicit deallocation event.

# 2.2 Programming Language

We now present a core calculus that is representative of the Multicore OCaml programming language. It is equipped with a dynamic thread creation operation and with the two kinds of memory locations presented earlier. For simplicity, we refer to this calculus as Multicore OCaml.

2.2.1 Syntax. The syntax of the calculus appears in Figure 3. It is a call-by-value  $\lambda$ -calculus, equipped with recursive functions, primitive operations on Boolean and integer values, tuples, and standard control constructs, including conditionals and sequencing. This calculus is extended with shared-memory concurrency, as follows. First, the construct fork *e* spawns a new thread. In the parent thread, this operation immediately returns the unit value (). In the new thread, the expression *e* is executed, and its result is discarded. Second, the language supports the standard operations of allocation, reading, and writing, on both nonatomic and atomic memory locations. In addition, atomic memory locations support a compare-and-set (CAS) operation.<sup>1</sup>

96:6

<sup>&</sup>lt;sup>1</sup>In the surface language, nonatomic locations have type 'a ref. Their operations are ref, !, and :=. Atomic locations have type 'a Atomic.t. Their operations are Atomic.make, Atomic.get, Atomic.set, and Atomic.compare\_and\_set.

$$\begin{array}{cccc} \operatorname{new}_{\operatorname{na}} v \xrightarrow{\operatorname{alloc}(a,v)} a & \mathop{!}_{\operatorname{na}} a \xrightarrow{\operatorname{rd}(a,v)} v & a \coloneqq_{\operatorname{na}} v \xrightarrow{\operatorname{wr}(a,v)} () & \operatorname{new}_{\operatorname{at}} v \xrightarrow{\operatorname{alloc}(A,v)} A \\ \\ \mathop{!}_{\operatorname{at}} A \xrightarrow{\operatorname{rd}(A,v)} v & A \coloneqq_{\operatorname{at}} v \xrightarrow{\operatorname{wr}(A,v)} () & & & & \\ \hline & & & & \\ \operatorname{CAS} A v_1 v_2 \xrightarrow{\operatorname{rd}(A,v_0)} \text{false} & & & & \\ \operatorname{CAS} A v_1 v_2 \xrightarrow{\operatorname{rd}(A,v_1,v_2)} \text{false} & & & \\ & & & & \\ \operatorname{CAS} A v_1 v_2 \xrightarrow{\operatorname{rdwr}(A,v_1,v_2)} \text{true} & & & \\ \end{array}$$

Fig. 4. Thread-local reduction:  $e \xrightarrow{m} e', e'_1, \dots, e'_n$  (selected rules)

$$\frac{e \xrightarrow{m} e' \quad \sigma; \mathcal{W} \xrightarrow{m} \sigma'; \mathcal{W}'}{\sigma; p_1, \langle e, \mathcal{W} \rangle, p_2} \qquad \qquad \underbrace{e \xrightarrow{\varepsilon} e', e'_1, \dots, e'_n}_{\sigma; p_1, \langle e, \mathcal{W} \rangle, p_2} \qquad \qquad \underbrace{\sigma; p_1, \langle e, \mathcal{W} \rangle, p_2}_{\Rightarrow \sigma; p_1, \langle e', \mathcal{W} \rangle, p_2, \langle e'_1, \mathcal{W} \rangle, \langle e'_n, \mathcal{W} \rangle}_{\Rightarrow \sigma; p_1, \langle e', \mathcal{W} \rangle, p_2, \langle e'_1, \mathcal{W} \rangle, \langle e'_n, \mathcal{W} \rangle}$$

Fig. 5. Thread-pool reduction:  $\sigma; p \Longrightarrow \sigma'; p'$

2.2.2 Operational Semantics. The "per-thread" reduction relation  $e \xrightarrow{m} e', e'_1, \ldots, e'_n$ , describes how an expression e takes a step and reduces to a new expression e', possibly interacting with the memory subsystem via an event m, and possibly spawning a number of new threads  $e'_1, \ldots, e'_n$ . The bulk of the rules that define this reduction relation form a standard small-step reduction semantics for call-by-value  $\lambda$ -calculus. These rules do not involve an interaction with the memory subsystem and do not spawn new threads. We omit them. In Figure 4, we present the reduction rules for the memory access operations, which interact with the memory subsystem via a memory event, and the reduction rule for "fork", which spawns one new thread.

In Figure 5, we define the "thread-pool" reduction relation  $\sigma; p \implies \sigma'; p'$ , which describes how the machine steps between two configurations  $\sigma; p$  and  $\sigma'; p'$ . In such a configuration,  $\sigma$  is a store, while p is a thread pool, that is, a list of threads, where each thread  $\langle e, W \rangle$  is a pair of an expression e and a view W. The left-hand rule allows the per-thread execution system and the memory subsystem to synchronize on an event m. The right-hand rule shows how new threads are spawned; a newly-spawned thread inherits the view of its parent thread. Because a per-thread reduction step cannot both access memory and spawn new threads, these two rules suffice.

The operational semantics of Multicore OCaml is the reflexive transitive closure of the threadpool reduction relation. It is therefore an interleaving semantics, albeit not a sequentially consistent semantics, as it involves a store whose behavior is nonstandard.

A machine configuration  $\sigma$ ; *p* is considered *stuck* if the thread pool *p* contains at least one thread that cannot take a step yet has not reached a value. A stuck configuration represents an undesirable event, a runtime error. There are many ways of constructing stuck configurations: examples include applying a primitive operation to arguments of incorrect nature, attempting to call a value other than a function, and so on. All such errors are ruled out by the OCaml type system:<sup>2</sup> the execution of a well-typed program cannot lead to a stuck configuration. Although this claim does not appear to have been formally established, it seems clear that a syntactic proof of type soundness for ML with references [Wright and Felleisen 1994] can be adapted to the semantics of Multicore OCaml.

A careful reader might note that a nonatomic read instruction (MEM-NA-READ) *could* potentially be stuck under certain circumstances. This could be the case, for instance, if the history *h* is empty,

<sup>&</sup>lt;sup>2</sup>No changes to the type system are required by the move from OCaml to Multicore OCaml. The type 'a Atomic.t is a new (primitive) abstract type.

or if the time stamp W(a) is too high, causing all write events in *h* to be considered outdated. In reality, though, neither of these situations can arise, because only a subset of *well-formed* machine configurations can be reached. In a well-formed configuration, every nonatomic location ever allocated must have a nonempty history, and no thread can get hold of an unallocated location, thereby removing the concern that *h* might be empty. Furthermore, a well-formed configuration must satisfy the following *global view invariant*: there exists a *global view* G such that:

- (1) every thread's view W is contained in G, that is,  $\forall \langle e, W \rangle \in p$ .  $W \sqsubseteq G$  holds;

- (2) the view of an atomic location is contained in  $\mathcal{G}$ , that is,  $\forall (A, \langle v, V \rangle) \in \sigma_{at}$ .  $\mathcal{V} \sqsubseteq \mathcal{G}$  holds;

- (3) the global view maps every nonatomic location to a time stamp that exists in the history of this location, that is, ∀(a, h) ∈ σ<sub>na</sub>. G(a) ∈ dom h holds;

- (4) the global view maps every currently unallocated location to the time stamp 0, that is,  $\forall a \notin \text{dom } \sigma_{\text{na}}$ .  $\mathcal{G}(a) = 0$  holds.

One can check that this is an indeed an invariant (i.e., it is preserved by every reduction step) and that this invariant implies that a nonatomic read instruction cannot be stuck. In fact, in the next section, we must prove this claim, and exploit this invariant, otherwise we would be unable to prove that our logic is sound: a sound program logic must guarantee that a verified program cannot get stuck. Thus, when we instantiate Iris for Multicore OCaml, we build the global view invariant into our "state interpretation" invariant (§3.1), and when we establish the reasoning rule for nonatomic read instructions (rule BASE-NA-READ in Figure 6), we exploit it (§3.3).

# 3 A LOW-LEVEL LOGIC: BASECOSMO

In this section, we set up a program logic for Multicore OCaml, based on the operational semantics presented in the previous section. To do so, we rely on Iris [Jung et al. 2018b], a generic framework for building program logics. Iris is not tied to a particular programming language or calculus. Its lower layer, the Iris base logic [Jung et al. 2018b, §3–5], is a purely logical construction. Its upper layer, the Iris program logic [Jung et al. 2018b, §6–7], is parameterized with a programming language. In order to instantiate it, a client must provide the following information:

- A set of "expressions".

- A subset of "values".

- A set of machine "states". For instance, a state might be a store, that is, a map whose domain is the set of all currently allocated memory locations.

- An operational semantics, in the form of a "per-thread step relation". This relation relates an expression and a state to an expression and a state and a list of expressions, which represent newly-spawned threads.

- A "state interpretation" predicate  $S : STATE \rightarrow IPROP$ .<sup>3</sup> This predicate represents a global invariant about the machine state. It typically relates the state with a piece of ghost state whose monoid structure<sup>4</sup> is chosen by the client so as to justify splitting the ownership of the machine state in certain ways.

Once the client has provided this information, the framework yields a program logic, that is,

- A weakest-precondition predicate wp  $e \{\Phi\}$ .

- A Hoare triple  $\{P\} e \{\Phi\}$ , which is just sugar for  $\Box (P \twoheadrightarrow wp e \{\Phi\})$ .

- An adequacy theorem, which states that if a closed program *e* satisfies the triple {True}  $e {\Phi}$  then it is safe to run, that is, its execution will not lead to a stuck configuration.

<sup>&</sup>lt;sup>3</sup>IPROP is the type of Iris assertions.

<sup>&</sup>lt;sup>4</sup>For simplicity, we use the word "monoid" everywhere, although "partial commutative monoid" would be more explicit, and an even more accurate term would be "resource algebra" [Jung et al. 2018b, §2.1] or "camera" [Jung et al. 2018b, §4.4].

• A set of programming-language-independent deduction rules for triples. These include the consequence rule, the frame rule, rules for allocating and updating ghost state, rules for setting up and exploiting invariants, and so on.

It is then up to the client to perform extra programming-language-specific work, namely:

- Define programming-language-specific assertions, such as "points-to" assertions.

- Prove entailment laws describing, e.g., how points-to assertions can be split and combined.

- Establish programming-language-specific deduction rules for triples, e.g., axioms that give triples for reading and writing memory locations.

We now apply this recipe to Multicore OCaml. This yields BaseCosmo, a logic for Multicore OCaml.

#### Instantiating Iris for Multicore OCaml 3.1

We begin instantiating Iris as follows:

- An "expression" is a pair  $\langle e, V \rangle$  of a Multicore OCaml expression and a view.

- Accordingly, a "value" is a pair  $\langle v, V \rangle$  of a Multicore OCaml value and a view.

- A "state" is a store  $\sigma$ , that is, a pair ( $\sigma_{na}, \sigma_{at}$ ) of a nonatomic store  $\sigma_{na}$  and an atomic store  $\sigma_{at}$ .

- The "per-thread step relation" is as defined in Figure 4.

To complete this instantiation, there remains to define a suitable "state interpretation" invariant S. In choosing this definition, we have a great deal of freedom. Our choice is guided by several considerations, including the manner in which we wish to allow splitting the ownership of the state, and the invariants about the state that we wish to keep track of. In the present case, we have the following two independent concerns in mind:

- We wish to allow splitting the ownership of memory locations (including nonatomic and atomic memory locations) under a standard "fractional permissions" regime.

- We need to keep track of the global view invariant (§2.2.2) enjoyed by the operational semantics of Multicore OCaml, because this invariant is required to justify that a nonatomic read instruction cannot be stuck.

With these goals in mind, we define our state interpretation invariant as follows. We give the definition first, then recall the Iris-specific notation used in this definition. We delay an explanation of the definition to the next subsection (\$3.2).

- Let γ<sub>na</sub> be a ghost location storing an element of AUTH(Loc<sub>NA</sub> fin→ AG(HIST) × FRAC).

Let γ<sub>at</sub> be a ghost location storing an element of AUTH(Loc<sub>AT</sub> fin→ AG(VAL × VIEW) × FRAC).

- Let  $\gamma_{gv}$  be a ghost location storing an element of AUTH(VIEW).<sup>5</sup>

- We define the state interpretation invariant as follows:

$$S(\sigma_{na},\sigma_{at}) \triangleq \begin{bmatrix} \bullet \sigma_{na} \end{bmatrix}^{\gamma_{na}} * \begin{bmatrix} \bullet \sigma_{at} \end{bmatrix}^{\gamma_{at}} * \exists \mathcal{G}. * \begin{cases} \begin{bmatrix} \bullet \mathcal{G} \end{bmatrix} \\ \forall \langle A, \langle v, V \rangle \rangle \in \sigma_{at}. V \sqsubseteq \mathcal{G} \\ [\forall \langle a, h \rangle \in \sigma_{na}. \mathcal{G}(a) \in \text{dom } h ] \\ [\forall a \notin \text{dom } \sigma_{na}. \mathcal{G}(a) = 0 \end{bmatrix}$$

Let us briefly recall some Iris concepts and notation. The monoids mentioned above are built out of the standard Iris toolkit. An authoritative monoid  $AUTH(\cdot)$  [Jung et al. 2018b, §6.3.3] has both authoritative elements of the form  $\bullet$  a and fragmentary elements of the form  $\circ$  b. An authoritative element is intended to represent the full knowledge of something, and cannot be split: the composition  $(\bullet a_1) \cdot (\bullet a_2)$  is never valid. A fragmentary element is intended to represent partial knowledge, and can be split and joined: the composition  $(\circ b_1) \cdot (\circ b_2)$  is defined as  $\circ (b_1 \cdot b_2)$ . Because a fragment must be a part of the whole, the composition  $(\bullet a) \cdot (\circ b)$  is valid only if  $b \leq a$  holds, where  $\leq$

<sup>&</sup>lt;sup>5</sup>VIEW is the monoid of views equipped with the operation  $\sqcup$ . It is an idempotent monoid.

is the ordering induced by the monoid law. The finite map monoid  $\cdot \stackrel{\text{fin}}{\longrightarrow} \cdot$  has finite maps as its elements; composition is pointwise. The agreement monoid [Jung et al. 2018b, §3.1, §4.3] on histories AG(HIST) has histories *h* as elements. Its composition law requires agreement: that is,  $h \cdot h$  is *h*, and  $h_1 \cdot h_2$  is invalid if  $h_1$  and  $h_2$  differ. The fractional permission monoid FRAC has the fractions  $q \in \mathbb{Q} \cap (0, 1]$  as its elements and addition as its composition law. Note that, because the fraction 0 is excluded, the fraction 1 cannot be composed with any fraction. This reflects the intuitive idea that the fraction 1 represents exclusive ownership of something.

#### 3.2 Multicore OCaml-Specific Assertions

We have performed the first step described at the beginning of this section (§3): we have instantiated Iris for the operational semantics of Multicore OCaml and for a state interpretation of our choosing. This yields a weakest-precondition predicate wp  $\langle e, \mathcal{V} \rangle$  { $\Phi$ }; a triple {P}  $\langle e, \mathcal{V} \rangle$  { $\Phi$ }; an adequacy theorem, which guarantees that this triple is sound; and a set of programming-language-independent deduction rules for triples. There remains to perform programming-language-specific work. We define three custom assertions, namely the nonatomic and atomic "points-to" assertions and a "valid-view" assertion. Next (§3.3), we give a set of reasoning rules where these assertions appear.

*3.2.1* Nonatomic Points-to. We wish to be able to split up the ownership of the nonatomic store under a fractional permission regime. As usual [Boyland 2003; Bornat et al. 2005], the fraction 1 should represent exclusive read-write access, while a fraction q < 1 should represent shared read-only access. Furthermore, we wish to ensure that whoever owns a share of a nonatomic location has exact knowledge of its history.

For this purpose, we have placed the ghost-state-ownership assertion  $\begin{bmatrix} \bullet & \sigma_{na} \end{bmatrix}^{\gamma_{na}}$  in the state interpretation invariant (§3.1), and we now define the nonatomic points-to assertion as follows:

$$q \cdot a \rightsquigarrow_{\mathrm{na}} h \triangleq \left[ \circ \{ a \mapsto (h,q) \} \right]^{\gamma_{\mathrm{na}}}$$

What is going on here? On the one hand, the points-to assertion claims the ownership of a fragmentary element of the monoid  $AUTH(LOC_{NA} \xrightarrow{fin} AG(HIST) \times FRAC)$ . The notation  $\{a \mapsto (h, q)\}$  describes an element of the monoid  $LOC_{NA} \xrightarrow{fin} AG(HIST) \times FRAC$ . The notation  $\{a \mapsto (h, q)\}$  describes an element of the monoid  $LOC_{NA} \xrightarrow{fin} AG(HIST) \times FRAC$ : it is a singleton map, which maps the location *a* to the pair (h, q). On the other hand, the state interpretation invariant owns the authoritative element  $\bullet \sigma_{na}$  of the monoid  $AUTH(\ldots)$ .<sup>6</sup> This ties the nonatomic store  $\sigma_{na}$ , which is part of the physical machine state, with the state of the ghost location  $\gamma_{na}$ .

Now, recall that, from the coexistence of the elements • *a* and • *b*, one can deduce  $b \le a$  (§3.1). Thus, when a points-to assertion  $q \cdot a \sim_{na} h$  is at hand, one can unfold the definition of this assertion and get a fragmentary element •  $\{a \mapsto (h, q)\}$ . One can also briefly "open" the state interpretation invariant and see an authoritative element •  $\sigma_{na}$ . From their coexistence, one deduces  $\{a \mapsto (h, q)\} \le \sigma_{na}$ , that is, the singleton map of *a* to the pair (h, q) is indeed a fragment of the physical nonatomic store  $\sigma_{na}$ .

Here,  $\leq$  is the ordering induced by the composition law of the monoid  $\text{Loc}_{NA} \xrightarrow{\text{fin}} \text{Ag}(\text{Hist}) \times \text{Frac.}$ Because this law requires agreement of the history components and addition of the fraction components, one can read the assertion  $q \cdot a \sim_{\text{na}} h$  as representing the knowledge that the history of this location is *h* and the ownership of a *q*-share of the nonatomic memory location *a*.

This technique is not original: we follow the pattern presented by Jung et al. [2018b, §6.3.3, §7.3]. We omit the fraction q when it is 1. Thus, we write  $a \sim_{na} h$  for  $1 \cdot a \sim_{na} h$ .

<sup>&</sup>lt;sup>6</sup>The notation •  $\sigma_{na}$  involves an abuse of notation. In it,  $\sigma_{na}$  must be understood as an element of the monoid  $Loc_{NA} \xrightarrow{fin} AG(HIST) \times FRAC$ , which maps every location *a* in the domain of  $\sigma_{na}$  to a pair of the history  $\sigma_{na}(a)$  and the fraction 1.

3.2.2 Atomic Points-to. Regarding the atomic points-to assertion, we proceed essentially in the same manner. Earlier (§3.1), we have placed the assertion  $\left[ \bullet \sigma_{at} \right]^{\gamma_{at}}$  in the state interpretation invariant. We now define the atomic points-to assertion as follows:

$$q \cdot A \rightsquigarrow_{\mathrm{at}} \langle v, \mathcal{V} \rangle \triangleq \exists \mathcal{W}. \ [\mathcal{V} \sqsubseteq \mathcal{W}] \ast \left[ \circ \{A \mapsto (\langle v, \mathcal{W} \rangle, q)\} \right]^{\gamma_a}$$

As a result of these definitions, the assertion  $q \cdot A \rightarrow_{\text{at}} \langle v, \mathcal{V} \rangle$  claims the ownership of a *q*-share of the atomic memory location *A*, guarantees that the value stored at this location is *v*, and guarantees that the view stored at this location is at least  $\mathcal{V}$ .

By requiring the view  $\mathcal{W}$  stored at A to satisfy  $\mathcal{V} \sqsubseteq \mathcal{W}$ , as opposed to the equality  $\mathcal{V} = \mathcal{W}$ , we make the points-to assertion reverse-monotonic in its view parameter: that is, if  $\mathcal{V}_1 \sqsubseteq \mathcal{V}_2$  holds, then  $q \cdot A \sim_{\text{at}} \langle v, \mathcal{V}_2 \rangle$  entails  $q \cdot A \sim_{\text{at}} \langle v, \mathcal{V}_1 \rangle$ . This seems convenient in practice, as it gives the user a concise way of retaining partial knowledge of the view that is stored at location A.

As with nonatomic points-to assertions, we omit the fraction q when it is 1.

3.2.3 Validity of a View. The last part of the state interpretation invariant (§3.1) asserts the existence of a view  $\mathcal{G}$  such that items (2), (3) and (4) of the global view invariant hold (§2.2.2). It also includes the ghost-state-ownership assertion  $\left[ \bullet \mathcal{G} \right]^{\gamma_{gv}}$ . We now define the "valid-view" assertion as follows:

$$valid \mathcal{V} \triangleq \left[ \circ \overline{\mathcal{V}} \right]^{\gamma_{gv}}$$

The assertion *valid*  $\mathcal{V}$  guarantees that  $\mathcal{V}$  is a fragment of the global view, that is,  $\mathcal{V} \sqsubseteq \mathcal{G}$  holds. Because the VIEW monoid is idempotent (that is,  $\mathcal{V} \sqcup \mathcal{V} = \mathcal{V}$ ), this assertion is duplicable. Thus, it does not represent the ownership of anything. It represents only the knowledge that  $\mathcal{V}$  is a fragment of the global view.

A validity assertion appears in almost all of the reasoning rules that we present in the next subsection (§3.3). In other words, the rules effectively require (and allow) every thread to keep track of the fact that its current view is valid. This encodes item (1) of the global view invariant.

### 3.3 Multicore OCaml-Specific Axioms

There remains to give a set of Multicore OCaml-specific deduction rules that allow establishing Hoare triples. We present just the rules that govern the memory access operations; the rest is standard [Jung et al. 2018b, §6.2]. These rules appear in Figure 6.<sup>7</sup> They are "small axioms" [O'Hearn 2019], that is, triples that describe the minimum resources required by each operation. Each of them is just a single triple {*P*}  $\langle e, W \rangle$  { $\Phi$ }, which, for greater readability, we display vertically:

$$\frac{P}{\frac{\langle e, \mathcal{W} \rangle}{\Phi}}$$

The precondition *P* describes the resources required in order to safely execute the expression *e* on a thread whose view is  $\mathcal{W}$ . The postcondition  $\Phi$ , which takes a pair  $\langle v', \mathcal{W}' \rangle$  of a value and a new view as an argument, describes the updated resources that exist at the end of this execution, if it terminates. This is a logic of partial correctness.

The word "axiom" is used because each rule is just a fact of the form "triple", as opposed to an implication of the form "triple implies triple". This does *not* mean that we accept these rules without justification. Each "axiom" in Figure 6 is in reality a lemma that we prove.

Allocating a nonatomic memory location (BASE-NA-ALLOC) returns a memory location *a* and does not change the view of the current thread. The points-to assertion  $a \sim_{na} \{0 \mapsto v\}$  in the

<sup>&</sup>lt;sup>7</sup>For the sake of readability, we hide the "later" modalities that appear in these rules. See Jung et al. [2018b, §6.2] for details.

| base-na-Alloc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | BASE-AT-ALLOC                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| True                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | valid W                                                                                                                                                                                                                                                                                                                                                                                                      |

| $\langle new_{na} \; v, \mathcal{W} \rangle$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\langle new_{at} \; v, \mathcal{W}  angle$                                                                                                                                                                                                                                                                                                                                                                  |

| $\int \upsilon' = a$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $\lambda \langle v', \mathcal{W}' \rangle . \exists A. * \begin{cases} v' = A \\ \mathcal{W}' = \mathcal{W} \\ A \sim_{\mathrm{at}} \langle v, \mathcal{W} \rangle \end{cases}$                                                                                                                                                                                                                              |

| $\lambda \langle v', W' \rangle$ . $\exists a. * \{ W' = W \}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $\lambda \langle v', \mathcal{W}' \rangle$ . $\exists A. * \{ \mathcal{W}' = \mathcal{W} \}$                                                                                                                                                                                                                                                                                                                 |

| $\lambda \langle v', W' \rangle . \exists a. * \begin{cases} v' = a \\ W' = W \\ a \rightsquigarrow_{na} \{ 0 \mapsto v \} \end{cases}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $A \sim_{\mathrm{at}} \langle v, W \rangle$                                                                                                                                                                                                                                                                                                                                                                  |

| base-na-Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BASE-NA-WRITE                                                                                                                                                                                                                                                                                                                                                                                                |

| $q \cdot a \rightsquigarrow_{\mathrm{na}} h * valid W$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $a \sim_{\mathrm{na}} h * valid W$                                                                                                                                                                                                                                                                                                                                                                           |

| $\frac{q \cdot a \rightsquigarrow_{\mathrm{na}} h * valid \mathcal{W}}{\langle !_{\mathrm{na}} a, \mathcal{W} \rangle}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $\frac{\langle a :=_{\operatorname{na}} v, W \rangle}{\langle a :=_{\operatorname{na}} v, W \rangle}$ $\lambda \langle v', W' \rangle \cdot \exists t. * \begin{cases} t \notin \operatorname{dom} h \\ W(a) < t \\ v' = () \\ W' = W[a \mapsto t] \\ a \sim_{\operatorname{na}} h[t \mapsto v] \\ valid W' \end{cases}$                                                                                     |

| $ \frac{\lambda \langle v', W' \rangle}{\lambda \langle v', W' \rangle} \cdot \exists t. * \begin{cases} t \in \operatorname{dom} h \\ W(a) \leq t \\ v' = h(t) \\ W' = W \\ a \cdot a \sim_{\operatorname{po}} h \end{cases} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\int t \notin \mathrm{dom} h$                                                                                                                                                                                                                                                                                                                                                                               |