MAXIME LEGOUPIL, Aarhus University, Denmark JUNE ROUSSEAU, Aarhus University, Denmark AÏNA LINN GEORGES, MPI-SWS, Germany JEAN PICHON-PHARABOD, Aarhus University, Denmark LARS BIRKEDAL, Aarhus University, Denmark

WebAssembly offers coarse-grained encapsulation guarantees via its module system, but does not support fine-grained sharing of its linear memory. MSWasm is a recent proposal which extends WebAssembly with fine-grained memory sharing via handles, a type of capability that guarantees spatial and temporal safety, and thus enables an expressive yet safe style of programming with flexible sharing. In this paper, we formally validate the pen-and-paper design of MSWasm. To do so, we first define MSWasmCert, a mechanisation of MSWasm that makes it a fully-defined, conservative extension of WebAssembly 1.0, including the module system. We then develop Iris-MSWasm, a foundational reasoning framework for MSWasm composed of a separation logic to reason about known code, and a logical relation to reason about unknown, potentially adversarial code. Iris-MSWasm thereby makes explicit a key aspect of the implicit universal contract of MSWasm: robust capability safety. We apply Iris-MSWasm to reason about key use cases of handles, in which the effect of calling an unknown function is bounded by robust capability safety. Iris-MSWasm thus works as a framework to prove complex security properties of MSWasm programs, and provides a foundation to evaluate the language-level guarantees of MSWasm.

CCS Concepts: • Security and privacy  $\rightarrow$  Logic and verification; • Theory of computation  $\rightarrow$  Logic and verification; *Higher order logic*; Programming logic; Separation logic; *Formalisms*.

Additional Key Words and Phrases: WebAssembly, Wasm, MSWasm, Capabilities, Memory Safety, Encapsulation, Logical Relation

# **ACM Reference Format:**

Maxime Legoupil, June Rousseau, Aïna Linn Georges, Jean Pichon-Pharabod, and Lars Birkedal. 2024. Iris-MSWasm: Elucidating and Mechanising the Security Invariants of Memory-Safe WebAssembly. *Proc. ACM Program. Lang.* 8, OOPSLA2, Article 282 (October 2024), 29 pages. https://doi.org/10.1145/3689722

# 1 Introduction

WebAssembly (abbreviated Wasm) is the current industry standard to run applications efficiently in the browser [Haas et al. 2017], and is increasingly adopted in cloud computing (for example, Fastly's Compute@Edge [Fastly documentation 2022; Hickey 2020] and Fermyon's Spin [Butcher 2022]), in part thanks to its well-defined semantics and the high-performance implementations it enables. To rise up to the stringent security requirements of the web, Wasm promises not only sandboxing, but also several language-level security guarantees, including control flow integrity and coarse-grained

Authors' Contact Information: Maxime Legoupil, Aarhus University, Aarhus, Denmark, maxime@cs.au.dk; June Rousseau, Aarhus University, Aarhus, Denmark, june.rousseau@cs.au.dk; Aïna Linn Georges, MPI-SWS, Saarbrücken, Germany, algeorges@mpi-sws.org; Jean Pichon-Pharabod, Aarhus University, Aarhus, Denmark, jean.pichon@cs.au.dk; Lars Birkedal, Aarhus University, Aarhus, Denmark, birkedal@cs.au.dk.

This work is licensed under a Creative Commons Attribution 4.0 International License. © 2024 Copyright held by the owner/author(s). ACM 2475-1421/2024/10-ART282 https://doi.org/10.1145/3689722 memory safety at the level of its units of code distribution, *modules*. Each module can define a *linear memory* (or several, in Wasm 2.0), which is private by default, but which the module can explicitly export. In that case, any other module can import it, and thereby access it unrestrictedly. This unusually strong encapsulation guarantee that a non-exported memory cannot be affected by other modules [Rao et al. 2023] makes edge computing practical and lightweight [Clark 2019]: one can safely compose a module with untrusted, potentially adversarial library modules to perform tasks (image compression, etc.) on separate memories. However, sharing is an all-or-nothing affair: a linear memory is either completely private, or all of it is shared with every module. As pointed out by Lehmann et al. [2020], this means that many of the classical attacks against memory unsafe languages, targeting a finer granularity, also work against programs that are not specifically written to take advantage of module isolation of WebAssembly.

Thus, to take advantage of the memory isolation guarantees of Wasm, programs require either invasive changes to fit WebAssembly's module system even though programs are typically not written directly in WebAssembly, or rely on extensive copying (which is the approach taken by the Component Model [The Bytecode Alliance 2023a,b]).

To address this lack of flexibility, Disselkoen et al. [2019] and Michael et al. [2023] propose Memory-Safe WebAssembly (abbreviated MSWasm), a conservative extension of WebAssembly with a mechanism for fine-grained memory sharing in the form of capabilities [Dennis and Van Horn 1966; Wilkes and Needham 1979], which it calls *handles*, and which embody authority over ranges of a new kind of memory: *segment memory*. This design is inspired by the capability-enhanced CHERI hardware architecture [Woodruff et al. 2014], which has been shown to be targetable from C with lightweight code changes by relying on reasonable patches to production compilers [Memarian et al. 2016; Zaliva et al. 2024]. The expectation is that MSWasm programs respect much finer memory safety invariants than plain Wasm. However, as illustrated during the development of the CHERI capability hardware architecture, these security invariants are very brittle: a mistake in a single detail can invalidate all encapsulation guarantees [Bauereiss et al. 2022; Nienhuis et al. 2020], and prose specifications backed by mere testing do not provide the required level of assurance.

*Contributions.* In this paper, we complete the pen-and-paper definition of MSWasm to be a conservative extension of WebAssembly 1.0, and mechanise it in the Coq proof assistant as MSWasmCert, building on WasmCert [Watt et al. 2021]. On top of this precise language definition, we develop Iris-MSWasm, a program logic that extends Iris-Wasm [Rao et al. 2023] with capability reasoning. Using the assertion language of Iris-MSWasm, we formulate an unstated yet key part of the *universal contract* [Van Strydonck et al. 2019] of MSWasm: that all instructions respect *robust capability safety.* Robust capability safety, as demonstrated for object capabilities [Devriese et al. 2016; Swasey et al. 2017] and capability hardware architectures [Georges 2023; Georges et al. 2021a, 2022a, 2021b, 2022b; Skorstengaard 2019; Skorstengaard et al. 2018, 2019a,b], makes it tractable to reason about the combination of known code with unknown, potentially adversarial code. As such, it refines the original *memory safety* guarantee of MSWasm, which does not directly lend itself to prove integrity properties of local state.

With our definition in hand, we identify cases where the original prose description is imprecise, as well as a handful of minor typos. We then show that MSWasm satisfies robust capability safety, and illustrate it on key representative examples capturing fine-grained memory invariants, thereby validating the design of MSWasm to the level of rigour that it deserves. To our knowledge, this is the first proof of robust capability safety for an industrial language, and for a language of this size. Moreover, because our formulation of robust capability safety captures the behaviour of an arbitrary MSWasm module given the exports that the module has access to, we expect that it can be

used to reason about the combination of WebAssembly code compiled from a higher-level language with unknown code compiled to MSWasm.

In showing robust capability safety for a complete definition of MSWasm, we make the case that, in addition to the extensional behaviour of a formally defined operational semantics, *industrial-scale language definitions can and therefore should come with a formally stated universal contract backed by a machine-checked proof.*

In summary, our contributions are:

- MSWasmCert, a mechanised language definition of MSWasm.

- Iris-MSWasm, a mechanised program logic covering all the language constructs of MSWasm, and with a complete proof of soundness.

- A mechanised statement and proof of robust capability safety using a logical relation.

All the technical results have been proved in the Coq proof assistant, and our Coq development is available online (see Data Availability Statement).

*Outline.* In the rest of this section, we present capabilities/handles, illustrate their use on a running example ( $\S1.1$ ), and describe the attacker model that we consider ( $\S1.2$ ). We then present our precise semantics of MSWasm ( $\S2$ ), focusing on the differences to plain WebAssembly, and highlight how we complete the original prose semantics. We then describe our program logic and its assertion language ( $\S3$ ), which we then use for the main contribution of this paper: the definition and proof of robust capability safety of MSWasm ( $\S4$ ). We illustrate this property on a larger example ( $\S5$ ), and we finish with a discussion ( $\S6$ ).

# 1.1 Introduction to MSWasm via a Running Example

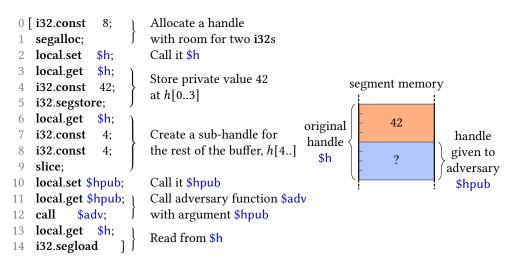

We illustrate MSWasm on the classic capability 'buffer' example [Woodruff et al. 2023], adapted to our setting. We give the code (using the formal syntax we present later in Figure 2) and depict it visually in Figure 1, and describe it informally below.

The known code starts (lines 0-2) by allocating a handle that has authority over a 'buffer': a part of segment memory. It stores (3–5) a private value, 42, in the first four bytes. The intent is to call an untrusted function, adv, with access to the rest of the buffer, but not to the private value. To do

so safely, the known code *slices* (6-9) the handle to get a sub-handle that has authority only over the rest of the buffer. The known code then calls adv, sharing only the sub-handle by passing it as an argument (11-12), and finally reads back the private value (13-14).

MSWasm guarantees that the handle \$h has not been freed and the private value is unchanged after the call to \$adv returns. In general, MSWasm guarantees fine-grained memory safety: unless explicitly given access to a handle with authority over a part of segment memory, a module cannot read or write to that part of segment memory.

In the rest of the paper, we show how to prove that this program's return value is either the **trap** failure value (in case the allocation or adversary call traps), or 42. We use a program logic to reason about the known code, and a logical relation to reason about the unknown code.

In §5, we also illustrate this approach on a stack module that showcases MSWasm and demonstrates that our approach scales to complex invariants about practical data structures.

# 1.2 Attacker Model and TCB

Wasm modules are linked together via *instantiation*. Instantiation does not take place within a Wasm program, but in a *host* — in the browser, this is typically JavaScript code. Instantiation enforces that all the modules are well-typed and have consistent exports and imports. The attacker model that we consider is one where one or more 'friendly' modules with known code are instantiated with one or more unknown, potentially adversarial Wasm modules. We assume that the host does not affect memories, locals, control flow, etc.; in our formalisation, we do this by restricting the host language. This attacker model fits the context of cloud computing (microservices, edge computing, etc.), where one client's module should be isolated from the third-party libraries it imports.

Our results concern the language specification, not a particular implementation in term of a Wasm runtime, which we still have to trust. We prove integrity, but not confidentiality — this could be tackled using a binary logical relation expanding our unary logical relation [Georges 2023, §4.5], but it is outside of our scope to define an operational semantics that faithfully captures confidentiality in the setting of WebAssembly. We also have to trust the host language to match the assumptions stated above. On the mechanisation side, we have to trust the soundness of the 'kernel' proof checker of the Coq proof assistant. Crucially, we do not need to trust the Iris separation logic framework, nor the separation logic rules we define, as they are linked to the operational semantics of MSWasm by our adequacy theorem (§3.4).

# 2 The MSWasmCert Semantics

Michael et al. [2023] present MSWasm as an extension of WebAssembly. While their pen-and-paper specification of MSWasm builds on a mostly faithful representation of WebAssembly, it remains an idealised version of the language. This results in a language specification that does not exactly line up with the official language specification of WebAssembly. Meanwhile, unlike most other industrial languages, one of the advantages of WebAssembly is that it has a detailed and comprehensive semantics [Haas et al. 2017], with a well-defined standard [Rossberg 2019]. One of our goals is thus to formalise the MSWasm proposal as an extension of the *official* and *complete* WebAssembly semantics. This is achieved by building our formalisation on top of the WasmCert mechanisation, which covers the full language as per the 1.0 specification.

#### 2.1 Plain Wasm Semantics

In this section, we briefly recall WebAssembly, highlighting the features omitted by Michael et al. [2023]; a reader familiar with the language can safely skip to §2.2. Figure 2 shows the syntax of WebAssembly, with the additions brought by MSWasm highlighted in magenta.

| (numeric type) $nt ::= i32   i64   f32   f64$<br>(value type) $t ::= nt   handle$<br>(value) $v ::= nt.const c   handle.const h$<br>(byte tag) $tag ::= Numeric   Handle$<br>(in the original presentation, these are called $\bigcirc$ and $\square$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (function type) $ft := ts \rightarrow ts$<br>(immediate)<br><i>i</i> , <i>min</i> , <i>max</i> , <i>addr</i> , <i>off</i> , <i>id</i> ::= N<br>(tagged byte) <i>tbyte</i> ::= <i>byte</i> × <i>tag</i> |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <pre>(handles) h ::= {base : addr, offset : off, bound : off, valid : bool, id : id } (basic instructions) b ::= nt.const c   t.add   other stackops   local.{get/set} i   global.{get/set} i   t.load (tp_sx)<sup>?</sup> a o   t.store tp<sup>?</sup> a o   memory.size   memory.grow   block ft bs   loop ft bs   if ft bs bs   br i   br_if i   br_table is   call i   call_indirect i   return   t.segload   t.segstore   segalloc   segfree   handle.add   slice (the flags of the load and store instructions represent a packed type, an alignment value and an offset. The new segload and segstore instructions do not have similar flags)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                        |  |  |  |  |

| (administrative instructions) $e := b \mid \text{handle.const } h \mid \text{trap} \mid \text{invoke } i \mid \text{label}_i \{es\} es \text{ end} \mid \text{local}_i \{F\} es \text{ end} \mid \text{call_host } tf hidx vs$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                        |  |  |  |  |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                        |  |  |  |  |

| $(\text{start}) \ \text{start} \ ::= \text{Some } i \mid \text{None}$ $(\text{function instances}) \ \text{finst} \ ::= \{(inst; ts); es\}_{tf}^{\text{NativeCl}} \mid \{hidx\}_{tf}^{\text{HostCl}}$ $(\text{table instances}) \ \text{tinst} \ ::= \{\text{elem} : is, \ \max : max^2\}$ $(\text{memory instance}) \ \text{minst} \ ::= \{\text{data} : bytes, \ \max : max^2\}$ $(\text{global instance}) \ \text{ginst} \ ::= \{\text{data} : bytes, \ \max : max^2\}$ $(\text{global instance}) \ \text{ginst} \ ::= \{\text{mut} : mutable^2, \ \text{value} : v\}$ $(\text{segment instance}) \ \text{sinst} \ ::= \{\text{segdata} : tbytes, \ \max : max^2\}$ $(\text{allocator instance}) \ \text{ainst} \ ::= id \rightarrow (addr \times off)^2$ $(\text{store}) \ S \ ::= \left\{ \begin{array}{c} \text{funcs} : \ \text{finsts}, \ \text{globs} : \ \text{ginsts}, \ \max : minsts, \ \text{tabs} : \ \text{tinsts}, \\ \text{seg} : \ \text{sinst}, \ \text{allocator} : \ \text{ainst} \\ (\text{frame}) \ F \ ::= \{\text{locs} : vs, \ \inf st : \ \text{inst} \} \\$ $(\text{module instance}) \ \text{inst} \ ::= \{\text{types} : \ \text{fts}, \ \text{funcs} : \ \text{is}, \ \text{globs} : \ \text{globs} : \ \text{globs} : \ \text{start} : \ s$ |                                                                                                                                                                                                        |  |  |  |  |

Fig. 2. WebAssembly Abstract Syntax in black, with the MSWasm additions in magenta

A Stack Language. WebAssembly code is given as a list of instructions, and its operational semantics works as a stack machine that reduces the head instruction. For example, the operational semantics rule for addition is defined as

$(S, F, [\mathbf{i32.const} c_1; \mathbf{i32.const} c_2; \mathbf{i32.add}]) \hookrightarrow (S, F, [\mathbf{i32.const} (c_1 + c_2)])$

(we explain S and F below). In order to apply this rule in the context of a larger program, WebAssembly provides structural rules that allow to reduce under a context. For example, if  $(S, F, es) \hookrightarrow (S', F', es')$ , then  $(S, F, vs + es + es_2) \hookrightarrow (S', F', vs + es' + es_2)$ , where we write vs for a list of values, and es for a list of expressions.

*The Store and the Frame.* WebAssembly operates over a *store* and a *frame*. The *store S* is a record that bookkeeps all globally available functions, memories, global variables, etc. The *frame F* contains the current function's local variables, as well as its *instance*. The instance symbolises the function's environment, describing which parts of the global store the function has access to. It is defined as a record which contains indices that refer to objects in the store. This means that functions access the store via a level of indirection through the frame.

The key role of the instance in the frame is visible for example in the **global.get** instruction:

$$\frac{F.\text{inst.globs}[i] = k}{(S, F, [\textbf{global.get } i]) \hookrightarrow (S, F, [v])}$$

All WebAssembly variables, as well as functions and all other objects are referred to with indices instead of names. For local variables, this index refers to the place in the list of local variables present in *F*.locs. However, for all other objects, because they may outlive the current function (and even the current module if they are exported), the value is kept in the store together with that of objects defined in other modules. The index into the store has to be looked up in the instance, *F*.inst. In the case of a global variable shown above, the instance's globs field is a list of indices into the store, the *i*-th of which corresponds to the location in the store of this module's *i*-th global variable. It is then from that location that we fetch the value of the variable from the store.

This indirection into the store via the frame is the crux of the coarse-grained encapsulation guarantees of WebAssembly. As we discuss in §2.2, handles achieve encapsulation very differently: they access the store directly, but are guarded by dynamic checks. The original presentation of MSWasm omits the instance from their description of the frame, and thus only accounts for handles. Meanwhile, our mechanisation captures both the coarse-grained encapsulation guarantees of WebAssembly, and the new fine-grained dynamic guarantees of handles.

*Modules and Host Language.* Frames and instances are constructed at runtime. Statically, Web-Assembly code is shipped in *modules*, each module defining functions, a linear memory, global variables, etc. A module can *import* any of those objects, either from another WebAssembly module that explicitly *export*ed it, or from the *host language* that runs the WebAssembly modules.

Static modules are turned into dynamic module instances via *instantiation*, in which the module's code is typechecked, its imports are satisfied, and its exports are prepared for subsequent imports. This process is not part of WebAssembly itself, and hence WebAssembly code always runs embedded in a *host language*, typically Javascript, that performs module instantiation and can also perform an array of other interactions with WebAssembly code, such as calling WebAssembly functions, accessing or modifying WebAssembly state, etc. The host language can also provide functions or other objects that WebAssembly modules can import. As with frame instances, the original MSWasm presentation omits any description of modules and module instantiation.

*Linear Memory.* One of the objects that a module can encapsulate is the *linear memory*. In WebAssembly, the *linear memory* of a module (which Michael et al. [2023] call *heap memory*) is a growable array of bytes. Linear memory is accessed via **load** and **store** instructions, which take an **i32** argument from the stack and treat it as an address. These instructions take a type as an immediate argument to know how many bytes to access and which encoding/decoding to use. WebAssembly defines two functions, serialise and deserialise, to encode and decode all four

numerical types. The **load** and **store** instructions can also take additional information (such as an offset) as immediate arguments to allow for simple pointer arithmetic. We show here a simple use of the **load** instruction, where the only immediate argument is the type to read:

$$\frac{F.\text{inst.mems}[0] = k}{(S, F, [i32.\text{const } c; t.\text{load}]) \hookrightarrow (S, F, [t.\text{const } c'])} \text{ deserialise}(t, bs) = c'}$$

Just like for the global variables, the index in the store of the current module's linear memory is looked up in the instance *F*.inst.<sup>1</sup>

*Typing*. WebAssembly 1.0 defines a simple type system with only four types: **i32**, **i64**, **f32** and **f64** (as we will see in §2.2, MSWasm introduces a new **handle** type). Instructions have type  $t1s \rightarrow t2s$ , where t1s is the types of the values expected on the stack by the instruction, and t2s is the types of the values that will be pushed on the stack. For example, t.add has type  $[t, t] \rightarrow [t]$  and t.load has type  $[i32] \rightarrow [t]$ , since addresses into memory are simple i32 integers in WebAssembly. The WebAssembly type system guarantees that well-typed programs satisfy progress and preservation.

#### 2.2 Segment Memory

In this section, we describe how MSWasm extends WebAssembly with a new kind of memory, *segment memory*, that is accessed not via **i32** integers interpreted as addresses, but via *handles*. More precisely, we present MSWasmCert – our formalisation of MSWasm in Coq – which adapts the prose description of MSWasm to a mechanisation of the full official 1.0 specification, and fixes some minor mistakes and limitations of the original prose definition.

*Handles.* MSWasm introduces new runtime values, handles, and a corresponding type, **handle**, which is distinct from the numeric types of WebAssembly. A handle is a form of fat pointer, represented as a record with the following fields : a base, an offset, a bound, a valid bit, and an id. The handle points to the bytes beginning at address (base + offset), its bounds of authority is described by the interval [base..base + bound), and its id is used to identify a handle based on its original allocation. Handles are unforgeable, and can only either be derived from other handles, or created when a segment is allocated by the **segalloc** instruction. In particular, this means that **handle.const** *h* cannot occur in the source program, it only appears at runtime. In MSWasmCert, we enforce this syntactically: as shown in Figure 2, handle constants are not basic instructions, i.e. instructions available to the programmer, but rather *administrative instructions*, i.e. instructions that only appear at runtime.

Dynamic Checks. A handle does not invariantly require its address base + offset to be within its bounds of authority [base..base + bound), thus allowing for common code patterns where a forbidden pointer might be created but never used (e.g. right before the end of a loop). Instead, instructions that seek to access the segment memory trigger *dynamic checks*, which guarantee that the accessed addresses are within the bounds of authority of the handle, that the validity bit is **true**, and that the handle's id is still live in the *allocator* (see below). If the conditions are met, the **segload** and **segstore** instructions are permitted to read and write from the *segment memory*. If the conditions are not met, the instructions reduce to **trap**. Just like the **load** and **store** instructions in linear memory, the **segload** and **segstore** instructions take a value type as an immediate argument to know how many bytes to read in the segment memory, and how to interpret these bytes.

$<sup>^{1}</sup>$ In WebAssembly 1.0, modules have at most one memory so the list *F*.inst.mems is of length at most one, hence the index at which we inspect it is always 0.

Storing Handles in Memory. One subtlety arises from reading handles. If no precautions are taken, a user could write a series of integer values into memory and then read them using handle.segload, effectively forging a handle. To prevent this, the bytes in segment memory are tagged as either Handle or Numeric. When reading a handle, if any of the involved bytes is tagged as Numeric, the read yields a handle with the validity bit set to false. MSWasm also mandates that reading and writing handles can only be done at addresses that are aligned with the length of a handle. This prevents forging a handle, which could otherwise be done by writing two handles consecutively in segment memory and reading from a tagged but unaligned address midway through the first. Since the bytes in linear memory are untagged, reading handles from it would be unsafe as this may forge a handle. Hence using the load instruction to read a handle from linear memory automatically traps. If handles must be stored and loaded, this can be done safely in segment memory by using the segstore and segload instructions.

In MSWasmCert, we abstract over what mechanism is used to serialise a handle into a byte representation, and simply assume we are provided two functions serialise\_handle and deserialise\_handle.

*Operations on Handles.* Two new instructions allow for manipulating handles: handle.add adds to the offset of a handle, changing its address, while slice restricts its bounds of authority. Neither operation increases the *authority* of a handle, and thus both are safe. In both cases, the id stays the same, thus uniquely identifying the handle across changes: all handles that share the same id are all derived from one original handle. Accordingly, freeing one handle (see below) will simultaneously free all handles with the same id.

*Modules.* The original pen-and-paper description of MSWasm [Michael et al. 2023] implicitly assumes that all programs run in the same module, and thus altogether omits any mention of WebAssembly modules (although their implementation reuses rWasm's support for modules). In MSWasmCert, we formally account for the full module system of WebAssembly. To do this, we need to decide how the coarse-grained encapsulation properties of the WebAssembly module system ought to interact with the fine-grained encapsulation properties of MSWasm handles. Rather than operating over several coarsely encapsulated segment memories, we choose to limit the store to a single segment memory shared between all modules. This simplifies the design, and makes it seamless to share a handle from one module to another.<sup>2</sup> This also underlines that the encapsulation properties no longer stem from WebAssembly's module system, but from the handles themselves providing fine-grained memory safety.

*Allocator.* Handles can be dynamically allocated and freed. While a handle grants spacial authority over the fragment of segment memory described in its metadata, the handle itself does not express whether that region is still temporally valid, or has already been freed. Instead, MSWasm keeps track of live handles using an *allocator.* Michael et al. [2023] state that the allocator should have an 'allocation' and a 'free' function, and describe some of their expected properties. In MSWasmCert, we define the allocator as a map from handle ids to either None, meaning a handle that has been freed, or Some pair of integers representing the handle's original base address and bound. Allocating a handle is modelled by extending the map, and freeing a handle is modelled by updating its mapping to None. The programmer can perform these operations by using the **segalloc** and **segfree** instructions. Allocation is non-deterministic: the handle returned by the **segalloc** instruction could point to any non-live part of segment memory. We impose several (slightly different from Michael et al. [2023]) conditions on the handle to be freed: its base and bound fields must be the original address and bound the handle got allocated as (i.e. the handle cannot have been sliced), its offset must be zero, and its validity bit must be **true**.

<sup>&</sup>lt;sup>2</sup>Related questions arise in the context of capability machines featuring virtual memory [Watson et al. 2023, §3.11.3].

$\begin{aligned} & \operatorname{aligned}(a, b) \triangleq a \mod b = 0 \\ & \operatorname{compatible}(addr, off, ainst) \triangleq \forall id \ addr' \ off'. ainst(id) = \operatorname{Some}(addr', off') \implies \\ & (addr + off \leq addr' \lor addr \geq addr' + off') \end{aligned}$   $\begin{aligned} & addr \leq \operatorname{length}(sinst.\operatorname{segdata}) \quad ainst(id) = \operatorname{None} \quad \operatorname{compatible}(addr, off, ainst) \\ & sinst' = \{\operatorname{segdata} = sinst.\operatorname{segdata}[addr..addr + off := 0], \ \max = sinst.\operatorname{max}\} \\ & ainst' = ainst[id \mapsto \operatorname{Some}(addr, off)] \end{aligned}$

We do not require that  $addr + off \le length(sinst.segdata)$ , so in cases like addr = length(sinst.segdata), we are actually growing the segment memory by appending zeros at the end.

$\frac{ainst(id) = \text{Some}(addr, bound)}{\langle sinst, ainst \rangle} \xrightarrow{\text{sfree}(addr, bound, id)} \langle sinst, ainst' \rangle} \langle sinst, ainst' \rangle$

Operational Semantics. The operational semantics rules for MSWasmCert are presented in Figure 4. These rules are almost identical to those of Michael et al. [2023], with the changes brought by MSWasmCert highlighted in indigo. We describe these changes below. For brevity, we do not include failure rules, which dictate that **segload**, **segstore**, **segfree**, **handle.add** and **slice** all reduce to the failure value **trap** if the premises to apply the successful rule are not met. We also provide in Figure 3 our own definitions for the  $\langle sinst, ainst \rangle \xrightarrow{salloc(addr,off,id)} \langle sinst', ainst' \rangle$  predicates used in the allocation and freeing rules.

The changes in the reduction rules from MSWasm to MSWasmCert are:

- MSWasmCert introduces a second operational semantics rule for **segalloc**, allowing the allocation to non-deterministically fail, to account for realistic machine behaviour.

- MSWasmCert adds an extra check on the **handle.add** operation to ensure that the new offset is non-negative. This is a design choice that allows us to use unsigned integers to represent offsets, and means that the check for non-negativity of offset in the rules for **segload** and **segstore** are now vacuous in MSWasmCert and can be removed.

- MSWasmCert enforces that freeing a handle must be done with the original handle, not a sliced version of it (the prose definition mandated that the base address must be the original address, but did not enforce that the bound must be the original bound). This is a design choice that we have found convenient when defining our program logic, and it allows for a programmer to easily create a non-freeable handle.

- MSWasmCert fixes two minor typos from the original work [Michael et al. 2023]: the higher bound check in the **segload** and **segstore** rules should be  $a \le$  instead of a < (otherwise, when allocating *n* spaces of memory, one cannot read a value that has size *n*), and the bound check for the second component of **slice** should be stricter since the bound is an offset from the base rather than an address: changing the base always needs to be compensated by lowering the bound.

Fig. 4. Operational semantics for the new instructions in MSWasm, phrased in the syntax of MSWasmCert. The non-cosmetic changes brought by MSWasmCert to MSWasm are highlighted in indigo. Clauses made redundant by our mechanisation are crossed out.

Proc. ACM Program. Lang., Vol. 8, No. OOPSLA2, Article 282. Publication date: October 2024.

*Buffer Example.* Let us come back to the buffer example from §1.1. We assume function \$adv has type [handle]  $\rightarrow$  [], but nothing more: it could be imported from another module and we might not know or trust its code. Since we do not share \$h with this function, we expect the return value of this program to be 42. In the next section, we present a program logic that lets us prove this.

#### 3 Program Logic

In order to reason about programs written in MSWasm, we define a program logic, Iris-MSWasm. Our program logic allows us to specify and verify known programs, and lays the foundations for defining the logical relation in §4, which allows to reason about interactions with unknown code.

Iris-MSWasm builds on top of Iris-Wasm [Rao et al. 2023], a program logic for WebAssembly, and on the Cerise family [Georges 2023; Georges et al. 2021a, 2022a, 2021b, 2022b; Skorstengaard 2019; Skorstengaard et al. 2018, 2019a,b] of program logics for an idealised capability machine inspired by CHERI. Iris-Wasm captures the coarse-grained encapsulation guarantees of plain WebAssembly, so building on it helps to highlight the differences to the fine-grained encapsulation guarantees we focus on. Building on top of Iris-Wasm also means that we inherit many properties like higher-orderness and the ability to reason about reentrant host calls. While mostly orthogonal to fine-grained memory safety, they can be desirable in many cases.

In this section, we recall Iris-Wasm, and then explain how we adapted it to MSWasm.

# 3.1 Iris-Wasm

Iris-Wasm [Rao et al. 2023] is a program logic for WebAssembly, defined in the Iris logical framework [Jung et al. 2018]. Instantiated with a language's operational semantics, Iris provides a program logic that allows to prove properties of programs, phrased in a higher-order separation logic. Atop the *structural rules* from Iris, we can derive *instruction-specific proof rules* for each instruction of the language. We can then use them to reason about WebAssembly code in a syntax-directed way.

*Logical Values.* We define *logical values*, noted *w*, to describe expressions that cannot reduce. These can be of several kinds. *Immediate values* **immV** *vs* represent a list of WebAssembly values. The *trap value* **trapV** represents a program that has safely halted execution. Iris-Wasm also defines other kinds of logical values because of WebAssembly's expressive control flow mechanisms. The original Iris-Wasm paper describes the treatment of these other logical values, which is unchanged in Iris-MSWasm.

Specifications. We phrase our proof rules and specifications using either *Hoare triples* or *weakest* precondition statements. The Hoare triple  $\{P\}$  es  $\{w, \Phi(w)\}$  means that "if the precondition P holds, the expression es executes safely while maintaining all invariants, and if it terminates on a logical value w, the predicate  $\Phi$  holds of that value w". A weakest precondition wp es  $\{w, \Phi(w)\}$  is a separation logic proposition that means "we hold precisely the resources necessary to run es safely and without breaking invariants, and if that run terminates on a logical value w, the predicate  $\Phi$  holds of that value w".

*Resources.* The Iris-Wasm program logic defines *resources* that describe ownership of the frame or ownership of fragments of the store; and weakest precondition rules corresponding to each instruction of WebAssembly, dictating what resources are needed to run each instruction. For example, the proof rule for *t*.load is given by (the coloured boxed are used to contrast with our

```

\begin{array}{ll} i \stackrel{\text{wm}}{\longrightarrow}_{addr} b & \text{Ownership of a byte in linear memory} \\ i \stackrel{\text{wms}}{\longmapsto}_{addr} bv & \text{Ownership of a list of bytes in linear memory} \\ \stackrel{\text{ws}}{\longrightarrow}_{addr} tb & \text{Ownership of a tagged byte in segment memory} \\ \stackrel{\text{ws}}{\longmapsto}_{addr} tbs & \text{Ownership of a list of tagged bytes in segment memory} \\ id \stackrel{\text{allocated}}{\longrightarrow}^{q} (addr, bound)^{?} & (Fractional) \text{ ownership of a handle id in the allocator} \\ i \stackrel{\text{wg}}{\longrightarrow} \{mutability; v\} & \text{Ownership of a global variable} \\ \stackrel{\text{Fr}}{\longrightarrow} F & \text{Ownership of the WebAssembly frame} \end{array}

```

Fig. 5. Points-to assertions corresponding to various components of the state

wp\_segload rule we introduce in §3.2):

| wp_load                                                         |                                                                                                            |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| $F.\text{inst.mems}[0] = n * n \xrightarrow{\text{wms}}_i bs =$ | $*  \text{deserialise}(t, bs) = v * \triangleright \Phi(\text{immV}[v]) * \stackrel{c}{\longrightarrow} F$ |

| wp [i32.const $i$ ; $t$ .load]                                  | $w, \Phi(w) \ast \stackrel{\text{FR}}{\longleftrightarrow} F \ast n \xrightarrow{\text{wms}}_i bs $        |

Taking  $\Phi(w) \triangleq w = \operatorname{immV}[v]$ , this means that if we own the frame resource  $\stackrel{FR}{\longrightarrow} F$  and the linear memory resource  $^{3} n \stackrel{\text{wms}}{\longrightarrow}_{i} bs$ , the load instruction executes safely. The *n* on the left-hand-side of the linear memory resource corresponds to the index of this module's memory in the store, looked up in the frame. If the instruction returns (which it does in this case), the return value is *v*, and we are handed back the frame resource  $\stackrel{FR}{\longrightarrow} F$  and the memory resources  $n \stackrel{\text{wms}}{\longrightarrow}_{i} bs$ . Figure 5 displays some of the resources of the Iris-Wasm program logic, with the new resources introduced by Iris-MSWasm highlighted in magenta.

In addition to reasoning about individual WebAssembly modules, Iris-Wasm also introduces a simple host language together with a program logic for it, making it possible to reason about multiple WebAssembly modules being sequentially instantiated by the host environment. The most important piece of this host language program logic is the *instantiation lemma*, that roughly states that if a module typechecks and we own resources corresponding all its imports, the module can be instantiated and we get resources corresponding to all objects (e.g. function closures, linear memories, global variables, etc.) created by the module.

Finally, Iris-Wasm is accompanied by a logical relation that allows to reason about unknown code. We describe our extension of this logical relation in detail in §4.

# 3.2 Iris-MSWasm

Our program logic, Iris-MSWasm, is defined by adapting Iris-Wasm to the features introduced by MSWasm. This entailed defining the logical ghost state for allocators and segment memories, defining new resources, and proving proof rules for all new instructions.

This constituted a non-trivial programming effort, as many of the new features behave very differently from the existing ones that have been implemented in Iris-Wasm. For example, in plain WebAssembly, all components of the store, including linear memories, grow monotonically during execution, so a simple heap can be used to represent them. But the segment memory can have parts of it freed, so a ghost map had to be used instead of a heap. Additionally, converting a linear memory to an index-map is as simple as mapping all indices from 0 to the size of the memory to

<sup>&</sup>lt;sup>3</sup>We use superscripts on the arrows (e.g. wms for the linear memory resource) to differentiate the various resources present in the program logic. Some resources like the frame resource additionally use a different arrow shape.

their corresponding byte. For the segment memory, only live addresses should point to a value, increasing the complexity of the definitions.

To accommodate for the new type of memory, we introduce new points-to resources, as described in Figure 5. The segment memory resource  $\stackrel{\text{ws}}{\longrightarrow}_{addr} tb$  represents ownership of a single tagged byte in segment memory. Allocator resources  $id \xrightarrow{\text{allocated}}^q$  None or  $id \xrightarrow{\text{allocated}}^q$  Some(addr, bound)represent fractional ownership of a handle id in the allocator. q is rational in (0, 1]. The case where q = 1 represents full ownership and allows to access or modify the value on the righthand-side of the arrow; in that case we may omit writing the fraction. If q < 1, the resource is only partially owned: the right-hand-side value can be accessed, but not modified. Since freeing a handle corresponds to updating its value in the allocator from Some (*base, bound*) to None, freeing requires full ownership, and we can use partial resources to symbolise handles that are unfreeable because they have been sliced. We also define a syntactic sugar for ownership of a list of tagged bytes *tbs* in segment memory:  $\stackrel{\text{wss}}{\xrightarrow}_{addr} tbs$ . Contrary to the resources for linear memory, there is no store index on the left-hand side of the arrow in the segment memory resources. This reflects the fact that all modules share one common segment memory.

Using theses new resources, we define and prove new weakest-precondition rules for all of MSWasm's new instructions. We present these new rules in Figures 6 and 7. These rules mirror the operational semantics introduced in §2.2. For example, the rule for *t*.segload is:

$$\begin{array}{c} t \neq \text{handle} & * & \stackrel{\text{wss}}{\longrightarrow} addr \ tbs \ * \ h.id \ \underline{allocated} \ \text{Some}(x) \ * \ h.offset + \text{sizeof}(t) \leq h.\text{bound} \ * \\ addr = h.\text{base} + h.offset * \ h.valid = \textbf{true} \ * \\ \hline deserialise(t, \text{untag}(tbs)) = v * \triangleright \Phi(\text{immV} [v]) * \stackrel{\text{FR}}{\leftarrow} F \\ \hline \text{wp [handle.const } h; t.\text{segload]} \left\{ w, \ \Phi(w) * \stackrel{\text{FR}}{\leftarrow} F \right\} * \stackrel{\text{wss}}{\vdash} addr \ tbs \ * \ h.id \ \underline{allocated} \ \text{Some}(x) \\ \end{array}$$

This rule is quite close to the wp\_load rule from §3.1. The differences are (1) the segment rule does dynamic checks to ensure the read is admissible, (2) the memory resource is a linear memory resource in the wp\_load rule but a segment memory resource in the wp\_segload rule (which also means that the premise looking up an index in the frame instance *F*.inst is unnecessary in the segment rule), and (3) the allocator resource is additionally present in the segment rule.

The premise  $t \neq$  handle in wp\_segload is required, because in the case of reading a handle from memory, additional checks are necessary and hence requires a separate wp\_segload\_handle rule, as displayed in Figure 6. A similar  $t \neq$  handle premise has to be added to wp\_load in Iris-MSWasm, since reading a handle from linear memory is not allowed in the MSWasm semantics. This is the only modification necessary to a rule from Iris-Wasm when defining Iris-MSWasm.

# 3.3 Specifying the Known Parts of the Buffer Example

Let us come back to the buffer example from §1.1, whose code is in Figure 1. In this section, we show how to reason about the known parts of its code, and we defer the discussion about the adversary call to §4.3. This explanation is quite technical, because we detail the entire proof. Its mechanisation can be found in our Coq development in file buffer\_code.v.

Our goal will be to prove that

$$\{ \underbrace{\overset{\mathrm{FR}}{\longleftrightarrow}} F \} \text{ buffer}_example \{ w, (\exists F', \underbrace{\overset{\mathrm{FR}}{\longleftrightarrow}} F') * (w = \operatorname{trapV} \lor w = \operatorname{immV} [i32.const \ 42]) \}$$

wp\_segload

$$t \neq \mathbf{handle} * \stackrel{\mathsf{wss}}{\longmapsto}_{addr} tbs * h.id \xrightarrow{allocated} q} \mathsf{Some}(x) * h.offset + sizeof(t) \leq h.bound * addr = h.base + h.offset * h.valid = true * deserialise(t, untag(tbs)) = v *

$$\diamond \Phi(\mathbf{immV} [v]) * \stackrel{\mathsf{FR}}{\longleftarrow} F$$$$

wp [handle.const h; t.segload]  $\left\{ w, \Phi(w) \ast \xrightarrow{wss}_{addr} tbs \ast h.id \xrightarrow{allocated}^{q} Some(x) \ast \xrightarrow{F_{R}} F \right\}$

wp\_segload\_handle

$t = \text{handle} \ast \vdash^{\text{wss}}_{addr} tbs \ast h.\text{id} \xrightarrow{allocated}^{q} \text{Some}(x) \ast h.\text{offset} + \text{sizeof}(t) \leq h.\text{bound} \ast$ aligned(addr, handle\_size)  $\ast b$  = allHandle(tags(tbs))  $\ast h_f$  = updateValid(h',  $b \land h'.\text{valid}) \ast$ addr = h.base + h.offset  $\ast h.\text{valid}$  = true  $\ast$  deserialise(t, untag(tbs)) = h'  $\ast$  $\diamond \Phi(\text{immV} [h_f]) \ast \stackrel{\text{FR}}{\leftarrow} F$

wp [handle.const h; t.segload]

$$\left\{ w, \Phi(w) \ast \xrightarrow{wss}_{addr} tbs \ast h.id \xrightarrow{allocated}^{q} Some(x) \ast \xrightarrow{F_{\mathsf{R}}} F \right\}$$

wp\_segload\_failure1

$$(h.offset + sizeof(t) > h.bound \lor h.valid = false \lor$$

$$(t = \text{handle} \land \neg \text{aligned}(h.\text{base} + h.\text{offset}, \text{handle_size}))) * \triangleright \Phi(\text{trapV}) * \stackrel{\mathsf{FR}}{\longleftrightarrow} F$$

wp [handle.const h; t.segload]

$$\left\{ w, \Phi(w) \ast \stackrel{\mathsf{FR}}{\longrightarrow} F \right\}$$

wp\_segload\_failure2

$$h.id \xrightarrow{allocated}^{q} None * \triangleright \Phi(trapV) * \stackrel{F_{R}}{\longleftrightarrow} F$$

wp [handle.const h; t.segload]  $\left\{ w, \Phi(w) * h.id \xrightarrow{\text{allocated}} \text{None} * \xrightarrow{F_{R}} F \right\}$

(We omit the similar failure rules for **segstore**, **segfree**, **handle**.**add** and **slice**; these rules are shown in our supplementary material)

Fig. 6. Iris-MSWasm rules for the segload instruction

where *F* is a frame where two local variables \$h and \$hpub are declared, both of type handle, and the instance contains a function \$adv of type [handle]  $\rightarrow$  []. Our desired post-condition allows the program to trap: this could correspond either to the allocation failing, or to the function call failing. Crucially, *trapping is safe*, as it ensures that no memory violation has occurred.

Since we focus here on reasoning about known code, we assume until the end of this section that we know a specification for function **\$adv**, say:

$$\forall h, q. \left\{ \begin{array}{c} \stackrel{\text{wss}}{\longrightarrow}_{h.\text{base}} \stackrel{-*}{\longrightarrow} \\ h.\text{id} \stackrel{\text{allocated}}{\longrightarrow}^{q} \text{ Some-} \end{array} \right\} [\text{handle.const } h; \text{call } \text{sadv}] \left\{ \begin{array}{c} w = \text{trapV} \lor \\ w = \text{immV} [] * \\ \exists tbs'. \stackrel{\text{wss}}{\longrightarrow}_{h.\text{base}} tbs' * \\ \exists opt. h.\text{id} \stackrel{\text{allocated}}{\longrightarrow}^{q} opt \end{array} \right\}$$

In other words, the function can be called on any handle input, as long as the caller has ownership of the segment memory region pointed by that handle. The function may trap, but if it does not, it yields back ownership of the same segment memory region upon return; the tagged bytes might

wp\_segstore

$t \neq \mathbf{handle} \ast \stackrel{\mathsf{wss}}{\longmapsto}_{addr} tbs \ast h.id \xrightarrow{allocated}^{q} \mathsf{Some}(x) \ast h.offset + \mathsf{sizeof}(t) \leq h.\mathsf{bound} \ast addr = h.\mathsf{base} + offset \ast h.\mathsf{valid} = \mathbf{true} \ast \mathbf{typeof}(v) = t \ast |bs| = \mathsf{sizeof}(t) \ast \mathsf{serialise}(t, v) = bs \ast \mathsf{addTag}(bs, \mathbf{Numeric}) = tbs' \ast \triangleright \Phi(\mathsf{immV}[]) \ast \stackrel{\mathsf{FR}}{\longleftrightarrow} F$

wp [handle.const h; v; t.segstore]

$$\left\{\begin{array}{cc} w, & \Phi(w) \ast \vdash^{wss}_{addr} tbs' \ast \\ & h.id \xrightarrow{allocated} g Some(x) \ast \stackrel{FR}{\leftarrow} F \end{array}\right\}$$

wp\_segstore\_handle

$t = \text{handle} \ast \vdash^{\text{wss}}_{addr} tbs \ast h.\text{id} \xrightarrow{\text{allocated}}^{q} \text{Some}(x) \ast h.\text{offset} + \text{sizeof}(t) \leq h.\text{bound} \ast addr = h.\text{base} + \text{offset} \ast h.\text{valid} = \text{true} \ast \text{aligned}(addr, \text{handle_size}) \ast |bs| = \text{sizeof}(t) \ast \text{serialise}(t, h') = bs \ast \text{addTag}(bs, \text{Handle}) = tbs' \ast \triangleright \Phi(\text{immV} []) \ast \xrightarrow{\text{FR}} F$

wp [handle.const h; handle.const h'; t.segstore]  $\begin{cases} w, & \Phi(w) * \vdash^{wss}_{addr} tbs' * \\ h.id \xrightarrow{allocated} q Some(x) * \stackrel{FR}{\leftarrow} F \end{cases}$

wp\_segfree

wp [handle.const h; segfree]

$$\left\{ w, \Phi(w) \ast \stackrel{F_{\mathsf{R}}}{\longrightarrow} F \right\}$$

wp\_segalloc

wp\_handleadd

$h' = \{\text{base} = h.\text{base}, \text{ offset} = h.\text{offset} + c, \text{ bound} = h.\text{bound}, \text{ valid} = h.\text{valid}, \text{ id} = h.\text{id}\} * h.\text{offset} + c \ge 0 * \triangleright \Phi(\text{immV} [\text{handle.const} h']) * \stackrel{c}{\leftarrow} \stackrel{F_{R}}{\longrightarrow} F$

wp [i32.const c; handle.const h; handle.add]  $\left\{ w, \Phi(w) \ast \stackrel{F_{R}}{\longleftrightarrow} F \right\}$

wp\_slice

$h' = \{ \text{base} = h.\text{base} + c_1, \text{ offset} = h.\text{offset}, \text{ bound} = h.\text{bound} - c_2, \text{ valid} = h.\text{valid}, \text{ id} = h.\text{id} \}$  $*0 \le c_1 < h.\text{bound} * c_1 \le c_2 * \triangleright \Phi(\text{immV} [\text{handle.const} h']) * \stackrel{\text{FR}}{\longleftarrow} F$

wp [handle.const h; i32.const  $c_1$ ; i32.const  $c_2$ ; slice]  $\left\{w, \Phi(w) \ast \stackrel{\mathsf{FR}}{\longrightarrow} F\right\}$

Fig. 7. Other Iris-MSWasm specific rules

have changed. We will return in §4.3 to the more general case where the function is completely untrusted and we are not given a specification for it.

Let us proceed instruction by instruction, recalling the resources we own at each point of the program. The resources displayed in gold are the ones necessary to fulfil premises of the next rule to be applied; the ones in black are unused and simply carried forward.

$$\{ \stackrel{\operatorname{FR}}{\longleftrightarrow} F \}$$

*Lines 0–1.* At the start, we only own the frame resource  $\hookrightarrow F$ . We can apply<sup>4</sup> rule wp\_segalloc from Figure 7 with

$$\Phi(w) \triangleq (\exists h.w = immV \text{ [handle.const } h] * (h.valid = false \lor (id \xrightarrow{allocated}) Some(h.base, n) * h.bound = n * h.offset = 0 * h.valid = true * \vdash^{wss}_{h.base} repeat(n, 0))))$$

(hence the wand implication in the first premise is a trivial  $P \rightarrow P$ ). To satisfy the second premise, we yield the resource  $\stackrel{F_R}{\longrightarrow} F$ . The post-condition gives us back the resource  $\stackrel{F_R}{\longrightarrow} F$ , and tells us that a value **handle.const** *h* has now been placed on the stack, and that either *h*.valid = **false** (representing a failed allocation), or we own the segment and allocator resources. If we define  $x \triangleq (h.\text{base}, h.\text{bound})$ , we have:

$$\left\{ \xrightarrow{FR} F * (h.valid = false \lor \xrightarrow{wss}_{h.base} repeat(8, 0) * h.id \xrightarrow{allocated} Some x \right\}$$

*Lines 2–3.* The next two instructions are **local.set** and **local.get**. Both instructions have corresponding proof rules in Iris-Wasm, which we apply sequentially. In both cases, the Iris-Wasm proof rule consumes the frame resource  $\xrightarrow{FR} F$  as a premise, and gives it back in the post-condition. **local.set** changes the frame to new one, F', where the value of local variable h is now h:

$$\left\{ \xrightarrow{F_{R}} F' * (h.valid = false \lor \longmapsto_{h.base} repeat(4 + 4, 0) * h.id \xrightarrow{allocated} Some x) \right\}$$

*Lines 4–5.* The next instruction is **segstore**. At this stage, we perform a case disjunction: if *h*.valid = **false** (i.e. the allocation has failed), then the failure rule wp\_segstore\_failure1 (the **segstore** equivalent of rule wp\_segload\_failure1 from Figure 6) applies since one of the dynamic checks fails. Hence we trap safely, and in this case we can conclude the whole proof here, as we have filled the first disjunct of the post-condition.

Let us now consider the second case: we own  $\vdash^{wss}_{h,base}$ repeat(8,0). We can apply rule wp\_segstore from Figure 7 with  $\Phi(w) \triangleq w = \operatorname{immV}[]$ . To fulfil the segment resource premise of the rule, we must yield the first half of the resource we hold. Thus we separate  $\vdash^{wss}_{h,base}$ repeat(8,0) into two resources  $\vdash^{wss}_{h,base}$ repeat(4,0) and  $\vdash^{wss}_{h,base+4}$ repeat(4,0). We yield the first of these (as well as the frame resource  $\stackrel{FR}{\longrightarrow} F'$  and our allocator resource) to satisfy the premises of wp\_segstore, and the latter is unused for this rule. The other premises are all the necessary dynamic checks, which are satisfied here, and the rules give us our resources back, having updated the tagged bytes in segment memory to now store our private value 42.

$$\{ \xrightarrow{\mathsf{Fr}} F' * \xrightarrow{\mathsf{wss}}_{h.\text{base}} \text{serialise}(\mathbf{i32}, 42) * \xrightarrow{\mathsf{wss}}_{h.\text{base}+4} \text{repeat}(4, 0) * h.\text{id} \xrightarrow{\text{allocated}} \text{Some } x \}$$

*Lines* 6-11. The next instructions are **local.get**, **slice**, **local.set** and **local.get** again. All of these instructions have associated proof rules: wp\_slice from Figure 7 for **slice**, and rules from Iris-Wasm for the local variables. The rule for **local.set** has changed the frame again to update the value of variable  $\frac{1}{7}$  of *h* that we obtained via slicing; we call *F*'' this new frame.

$\left\{ \xrightarrow{\text{FR}} F'' \ast \longmapsto_{h.\text{base}} \text{serialise}(\mathbf{i32}, 42) \ast \longmapsto_{h.\text{base}+4} \text{repeat}(4, 0) \ast h.\text{id} \xrightarrow{\text{allocated}} \xrightarrow{1/2+1/2} \text{Some } x \right\}$

<sup>&</sup>lt;sup>4</sup>We omit the structural rules that allow to bind the first instruction in order to apply the proof rule.

*Line 12.* Now, we come to the call to function **\$adv**. In our simplified setting, we have a specification, which we wish to apply. Since by definition h'.base = h.base + 4 and h'.id = h.id, we have all the resources needed to fill the precondition. If we apply the specification with q = 1, we must lose the entire allocator resource to fulfil the precondition of the specification, and we would only get back that there exists *opt* such that  $h.id \xrightarrow{allocated} opt$ . This would not allow us to later execute the **segload** instruction. Instead, we can separate our allocator resource into two partial resources  $h.id \xrightarrow{allocated} 1/2$  Some x. Now we can apply the specification with  $q = \frac{1}{2}$  yielding only one of our partial resources, and keeping the second.

The postcondition tells us that either the call has trapped (in which case we can terminate the proof like before), or there exists some tagged bytes *tbs'* and an option *opt* such that we now  $own \vdash ws \rightarrow_{h'.base} tbs'$  and *h.id*  $\xrightarrow{allocated} 1/2 opt$ . Combined with the partial resource we kept, we know that *opt* = Some *x*, and we can combine our two fragments to get a full allocator resource. Informally, that means that the handle is still allocated.

Importantly, the other handle is not required by the specification, and hence the segment resource  $\downarrow^{\text{wss}}_{h.\text{base}}$  serialise(i32, 42) is framed away.

$$\{ \xrightarrow{F_{R}} F'' * \xrightarrow{wss}_{h,base} \text{serialise}(i32, 42) * \xrightarrow{wss}_{h,base+4} tbs' * h, id \xrightarrow{allocated} \text{Some } x \}$$

*Lines 13–14.* Lastly, we use the Iris-Wasm rule for **local.get** to get the value of variable \$h, and rule wp\_segload from Figure 6 allows us to conclude that the return value is indeed 42 as expected.

In the next section, we show how we can achieve the same result when the function \$adv is not specified.

# 3.4 Adequacy

The Iris logical framework provides an *adequacy theorem* [Jung et al. 2018, §6.4] that relates the weakest precondition statement to the operational semantics. This means that Iris is not in our Trusted Computing Base, as holding a weakest precondition now implies a statement phrased entirely in terms of the operational semantics of MSWasmCert.

THEOREM 3.1 (ADEQUACY). If wp es  $\{w, \Phi(w)\}$  and  $(S, F, es) \hookrightarrow^* (S', F', vs)$  for some values vs, then  $\Phi(vs)$  holds.

Using the adequacy theorem, we can prove the following result for the buffer example from §1.1:

THEOREM 3.2 (BUFFER EXAMPLE). If the code in Figure 1 terminates, it terminates on either the trap value **trapV**, or on value 42

PROOF SKETCH. We begin by proving

$\{ \stackrel{\text{FR}}{\leftarrow} F \}$  buffer\_example  $\{ w, (\exists F', \stackrel{\text{FR}}{\leftarrow} F') * (w = \text{trapV} \lor w = \text{immV} [i32.\text{const } 42] ) \}$

We have shown in §3.3 how to reason about the known parts of the code, and we will show in §4.3 how to reason about the unknown code; hence we have the wanted Hoare triple. This proof can also be seen in our Coq development in file buffer\_code.v.

Then, we use the program logic for our host language to reason about the instantiation on the adversary module and the buffer module. The instantiation lemma provides the frame resource  $\xrightarrow{FR} F$  from the precondition of the Hoare triple. This yields the weakest precondition statement wp buffer\_instantiation { $w, w = trapV \lor w = immV$  [i32.const 42]}. A proof of this can be seen in our Coq development in file buffer\_instantiation.

Finally, we apply the adequacy theorem which yields the desired result. This entails carefully providing all of the resource algebras necessary to implement the logical state of Iris and use all

the ghost resources that Iris-MSW asm leverages. A mechanised proof can be seen in our Coq development in file <code>buffer\_adequacy.v.</code>  $\hfill \Box$

#### 4 Robust Capability Safety

We have described how to use Iris-MSWasm to reason about known code. What remains to verify a complete example is to explain how to reason about unknown, potentially adversarial code. More precisely, when proving the weakest precondition for the buffer example, we eventually reach the call to the unknown imported function. At that point, one of our proof obligation is to show the weakest precondition for the body of that function. Since the function is arbitrary, we cannot step through its instructions. And since the function is untrusted, we cannot simply assume that we are given a weakest precondition for it. Instead, we want to define a *universal* specification for unknown code, which gives an over-approximation of its behaviour in the form of a weakest precondition.

To that end, we define a logical relation for the MSWasm type system, and prove that it satisfies the fundamental theorem of logical relations. In essence, the logical relation defines what it means for a value to be *safe to share*, and an expression to be *safe to execute*. Our logical relation builds on the logical relation defined in Iris-Wasm [Rao et al. 2023], and follows the typical design of step-indexed logical relations [Ahmed 2004] in Iris [Krebbers et al. 2017; Timany et al. 2022], and applies the techniques used in the Cerise line of work [Georges et al. 2021a, 2022a,b]. We present the intuition behind our logical relation in §4.1, and then define it and show that it is sound in §4.2, and showcase how it gives us robust safety on our buffer example in §4.3.

# 4.1 Informal Intuition

The high-level idea behind our logical relation is to define what it means for a value to be *safe to share*, and an expression to be *safe to execute*. What this means depends on the type of the value or expression: for example, a handle is safe to share if it grants memory access to its range of authority (i.e. grants access to the relevant points-to predicates), and if that memory recursively contains values that are safe to share. Meanwhile, an expression *es* is safe to execute when there is a weakest precondition for it wp *es* {*w*, *w* is safe to share}. In this simplified definition, *es* either loops, or reduces to a value that is safe to share. The formal definition has to account for programs that reduce to **trapV**, as well as programs that either **return** or **break** to the surrounding context. Crucially, as described earlier, a program that reduces to **trapV** (say, because it failed a dynamic check) is safe to execute.<sup>5</sup>

The definitions of *safe to share* and *safe to execute* can be viewed as a *universal contract*, in the sense that it holds for all well-typed MSWasm programs. A key theorem is to prove that this is the case. We call this result the *fundamental theorem of the logical relation*: if a program *es* is a well-typed MSWasm program, then it is *safe to execute*. We state this theorem formally in §4.2.

By applying the fundamental theorem, since module instantiation guarantees that its functions are well typed, we can derive weakest precondition specifications for imported functions, even when they are unknown. The caveat is that in order to get this specification, any shared handle must *also* satisfy the universal contract, i.e. satisfy the value interpretation for handles. Thus, a key feature of the logical relation is to capture the fine-grained encapsulation properties of handles, so as not to impose invariants over segment regions that are *not* shared.

$<sup>^{5}</sup>$ As mentionned in 1.2, we only consider integrity properties. If we were to consider confidentiality properties, we would need to consider potential interoperability with IO

$\mathcal{V}[ts]$  : LogVal  $\rightarrow$  iProp

ValidHandleAddr(*addr*, *base'*, *bound'*)  $\triangleq$  aligned(*base'* + *addr*, handle\_size)  $\land$ 0  $\leq$  *addr*  $\land$  *addr* + handle\_size  $\leq$  *bound'*

$$\mathcal{V}_{0}[[\text{handle}]](v) \triangleq \exists h. v = \text{handle.const } h *$$

$$\begin{pmatrix} h.valid = \text{false } \lor \\ \exists \gamma, base', bound', base'', bound'', q. \\ [h.base..h.base + h.bound) \subseteq [base'..base' + bound') * (1) \\ [base'..base' + bound') \subseteq [base''..base' + bound'') * (2) \\ q \in \{\frac{1}{2}, 1\} * ((h.base = base'' * h.bound = bound'') \Longrightarrow q = 1) * (3) \\ \downarrow \circ (h.id \hookrightarrow (\gamma, base', bound'', q))^{\gamma_{\text{toks}}} * (4) \\ \exists tbs.|tbs| = bound' * \stackrel{\text{wss}}{\longmapsto}_{base'} tbs * \\ \forall addr. ValidHandleAddr(addr, base', bound') \rightarrow * \\ \begin{pmatrix} (\exists off. 0 \le off < \text{handle_size } \land \\ tbs[addr + off] = (-, \text{Numeric}) \end{pmatrix} \lor \\ \mathcal{V}_{0}[[\text{handle}](\text{handle.const} \\ deserialise_handle( \\ untag(tbs[addr..addr + handle_size]))) \end{pmatrix} \end{bmatrix} C_{\text{Inv}} \end{pmatrix}$$

$$\mathcal{V}_{0}[[t](v) \triangleq \exists c. v = t.\text{const } c \quad (\text{for } t \neq \text{handle}) \\ \mathcal{V}[[t_{1}, \cdots, t_{n}]](w) \triangleq w = \text{trapV} \lor \\ \exists v_{1}, \cdots, v_{n}. w = \text{immV} [v_{1}, \cdots, v_{n}] \land \mathcal{V}_{0}[[t_{1}](v_{1}) \land \cdots \land \mathcal{V}_{0}[[t_{n}]](v_{n}) \end{pmatrix}$$

Fig. 8. Our logical relation for values

### 4.2 Logical Relation

More formally, we define, for each type *t*, a predicate  $\mathcal{V}[\![t]\!]$  describing values that are safe to share, called the *value interpretation* of type *t*, and a predicate  $\mathcal{E}[\![t]\!]$  of expressions that are safe to execute, called the *expression interpretation* of type *t*.

The difficulty when defining a logical relation for a full industrial language is that one must define a logical interpretation for all objects of the language: not only values and expressions, but also frames, function closures, linear memories, instances, contexts, etc. Iris-Wasm defines a relation for each WebAssembly object. In this work, we extend it to interpret the new types introduced by MSWasm. In particular, we define new interpretations for handle values and allocators. To keep the explanations simple, we will primarily focus on these new logical relations, and refer to the Coq mechanisation for the full definition. That being said, the explanations are somewhat technical, and will assume some familiarity with various Iris concepts.